One-Stop-Servicer fir elektronesch Produktioun, hëllefen Iech einfach Är elektronesch Produkter vu PCB & PCBA z'erreechen

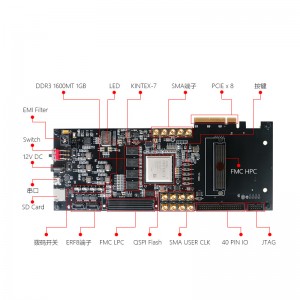

FPGA Xilinx K7 Kintex7 PCIe optesch Faserkommunikatioun

- DDR3 SDRAM: 16GB DDR3 64-Bit-Bus, Datenrate 1600 Mbps

- QSPI Flash: E Stéck 128mbit QSPIFLASH, dat fir FPGA Konfiguratiounsdateien a Benotzerdatenspäicherung benotzt ka ginn

- PCLEX8 Interface: Déi Standard PCLEX8 Interface gëtt benotzt fir mat der PCIE Kommunikatioun vum Computer-Motherboard ze kommunizéieren. Si ënnerstëtzt de PCI, Express 2.0 Standard. D'Eenkanal-Kommunikatiounsrate kann bis zu 5 Gbps erreechen.

- USB UART Serienport: E Serienport, verbënnt sech mam PC iwwer de MiniUSB Kabel fir seriell Kommunikatioun auszeféieren

- Micro SD Kaart: MicroSD Kaartesëtz ganz agebaut, Dir kënnt déi Standard MicroSD Kaart uschléissen

- Temperatursensor: en Temperatursensorchip LM75, deen d'Ëmwelttemperatur ronderëm d'Entwécklungsplat iwwerwaache kann

- FMC-Erweiderungsport: en FMC HPC an en FMCLPC, déi mat verschiddene Standard-Erweiderungskaarte kompatibel kënne sinn

- ERF8 High-Speed-Verbindungsterminal: 2 ERF8-Ports, déi ultra-High-Speed-Signaliwwerdroung ënnerstëtzen 40-Pin-Verlängerung: eng allgemeng Verlängerungs-IO-Interface mat 2,54 mm 40-Pin reservéiert, effektiv O huet 17 Puer, Ënnerstëtzung 3,3V

- Déi peripher Verbindung vum Niveau an dem 5V Niveau kann déi peripher Peripheriegeräter vun ënnerschiddlechen allgemengen 1O Schnëttstellen verbannen.

- SMA-Terminal; 13 héichwäerteg vergoldete SMA-Käpp, wat praktesch ass fir Benotzer fir mat High-Speed AD/DA FMC-Expansiounskaarten fir Signalerfassung a -veraarbechtung zesummenzeschaffen

- Taktverwaltung: Multitaktquell. Dozou gehéiert d'200MHz Systemdifferenztaktquell SIT9102

- Differentialkristall oszilléierend: 50MHz Kristall a SI5338P programméierbare Taktmanagementchip: och equipéiert mat

- 66MHz EMCCLK. Kann sech präzis un ënnerschiddlech Taktfrequenz upassen

- JTAG-Port: 10 Stéck 2,54 mm Standard-JTAG-Port, fir den Download an d'Debugging vun FPGA-Programmer

- Sub-Reset Spannungsüberwachungchip: e Stéck ADM706R Spannungsüberwachungchip, an de Knäppchen mam Knäppchen liwwert e globale Reset-Signal fir de System

- LED: 11 LED-Luuchten, weisen d'Stroumversuergung vun der Boardkaart un, config_done Signal, FMC

- Stroumindikatorsignal, an 4 Benotzer-LEDen

- Schlëssel a Schalter: 6 Schlësselen a 4 Schalter sinn FPGA-Reset-Knäppercher,

- De Programm B Knäppchen an 4 Benotzerknäppercher sinn zesummegesat. 4 Eenzelmesser Duebelschalter

Schreift Är Noriicht hei a schéckt se eis

Produktkategorien

-

Telefon

-

E-Mail

-

WhatsApp

-

Skype

-

Skype

-

Skype