Produkter

-

Industriell nei Atom D525 dc12v ugedriwwe Motherboard Industriell Motherboard ITX Motherboard mat PCI Motherboard Linux

Chipsatz: Intel NM10 High-Speed-Chipsatz

Prozessor: Integréierten Intel Atom D525 1.8G Prozessor

Frontend-Busfrequenz: Intel NM10 High-Speed-Chipsatz

Systemspeicher: 1*SODDRIII-Slot

(Ënnerstëtzt 800/1066 Späicher, bis zu 4GB)

BIOS: AMI 8MB DPI Flash-ROM

Audiofunktioun: Onboard ALC662 (6-Kanal HiFi Audio, MIC Line-Out Ënnerstëtzung)

Bus-Erweiderung: 1 PCI

Displayport: VGA-Port, an erweiderten VGA-Ausgangsport

Dimensiounen (LxB): 170mm x 170mm

SATA: Zwee SATAen déi 3GB/S ënnerstëtzen

Seriell Port: Zwee COM Ports, COM1/2:RS-232 Modus

Parallel Mond: 1 Brunnkapp

USB Ports: 8 USB2.0 Ports (4 Réckpanelen, 4 integréiert Pins)

PS/2 Interface: PS/2 Tastatur- a Maus-Interface (d'Board enthält 6-PIN Tastatur- a Mausreih-Pins)

Netzwierkport: Een RTL8105E 10/100M NIC, ënnerstëtzt disklos RPL oder PXE Boot, ënnerstëtzt Netzwierk-Wake-up

Display: GMA 3150 (CPU integréiert Grafik)

Soundkaart: ALC662 HD Soundkaart Line-Out, Mikrofon

Liwwert e Front Audio Pin

Stroumversuergungstyp: DC-12V

-

Raspberry Pi Liwwerant | Industriell Raspberry Pi

De Raspberry Pi ass e klenge Computer an der Gréisst vun enger Kreditkaart, dee vun der Raspberry Pi Foundation a Groussbritannien entworf an entwéckelt gouf, fir d'Informatikunterrecht ze fërderen, besonnesch a Schoulen, sou datt d'Schüler Programméierung a Computerkenntnisser duerch praktesch Praxis léiere kënnen. Obwuel de Raspberry Pi ufanks als edukativt Instrument positionéiert gouf, huet en duerch seng héich Flexibilitéit, säi niddrege Präis a seng mächteg Funktiounen séier Computerbegeeschterten, Entwéckler, Do-it-yourself-Enthusiasten an Innovateuren weltwäit iwwerzeegt.

-

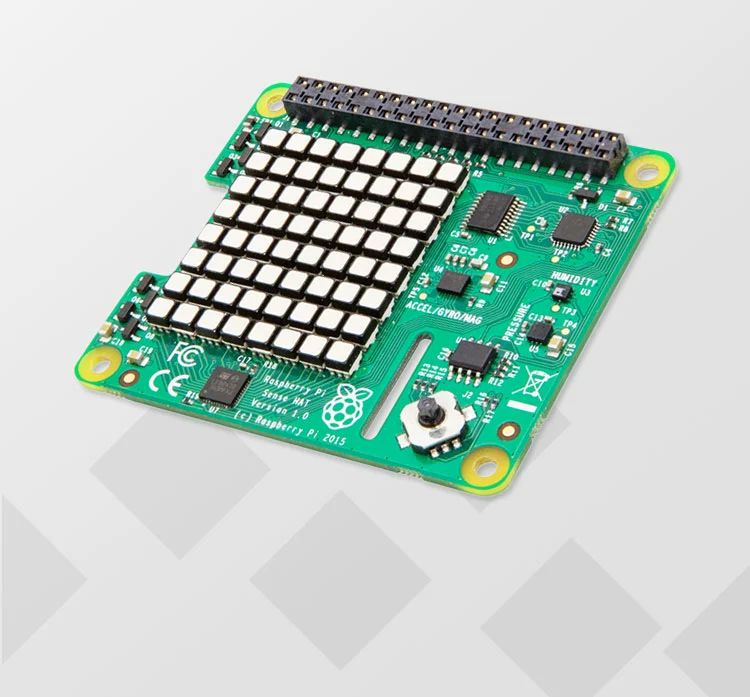

Raspberry PI Sense HAT

Offiziellen autoriséierten Distributeur vu Raspberry Pi, Äert Vertraue wäert!

Dëst ass eng originell Raspberry Pi Sensor-Erweiderungskaart, déi Gyroskope, Beschleunigungsmesser, Magnetometer, Barometer a Temperatur- a Fiichtegkeetssensore integréiere kann, souwéi agebaute Peripheriegeräter wéi eng 8×8 RGB LED-Matrix an eng 5-Wee-Wippschalter.

-

Raspberry Pi Zero W

De Raspberry Pi Zero W ass den neie Liebling vun der Raspberry PI Famill a benotzt dee selwechten ARM11-Core BCM2835 Prozessor wéi säi Virgänger, a leeft ongeféier 40% méi séier wéi virdrun. Am Verglach mam Raspberry Pi Zero huet en dee selwechte WIFI a Bluetooth wéi den 3B, wat un méi Beräicher ugepasst ka ginn.

-

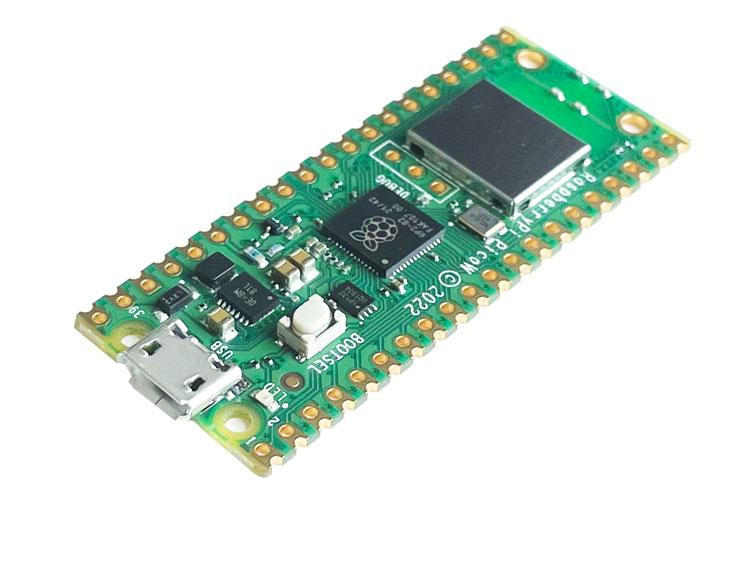

Raspberry Pi Pico Serie

Dëst ass déi éischt Mikrocontroller-Entwécklungsplatine baséiert op dem selwer entwéckelte Raspberry Pi Chip, deen den Infineon CYW43439 Wireless Chip ergänzt huet. De CYW43439 ënnerstëtzt IEEE 802.11b /g/n.

Ënnerstëtzung vun der Konfiguratiouns-PIN-Funktioun, kann d'Benotzer flexibel Entwécklung an Integratioun erliichteren

Multitasking dauert keng Zäit, an d'Bildspäicherung ass méi séier a méi einfach.

-

Raspberry Pi Zero 2W

Baséierend op der viregter Zero-Serie hält sech de Raspberry Pi Zero 2W un den Designkonzept vun der Zero-Serie, andeems en de BCM2710A1-Chip an 512 MB RAM op enger ganz klenger Platin integréiert an all Komponenten op enger Säit clever placéiert, wat et erméiglecht, sou eng héich Leeschtung an engem klenge Pak z'erreechen. Zousätzlech ass en och eenzegaarteg an der Hëtzofleedung, andeems en eng déck intern Kofferschicht benotzt fir d'Hëtzt vum Prozessor ze leeden, ouni sech iwwer héich Temperaturproblemer Suergen ze maachen, déi duerch héich Leeschtung verursaacht ginn.

-

Raspberry PI POE+ HAT

Ier Dir de PoE+ HAT installéiert, installéiert déi geliwwert Kofferpolen un de véier Ecker vun der Leiterplatte. Nodeems Dir de PoE+HAT un d'40Pin- a 4-Pin-PoE-Ports vum Raspberry PI ugeschloss hutt, kann de PoE+HAT iwwer en Netzwierkkabel fir d'Stroumversuergung an d'Netzwierkverbindung mam PoE-Gerät verbonne ginn. Beim Ofhuele vum PoE+HAT, zitt de POE+ Hat gläichméisseg, fir de Modul sanft vum Pin vum Raspberry PI ze léisen an de Pin net ze béien.

-

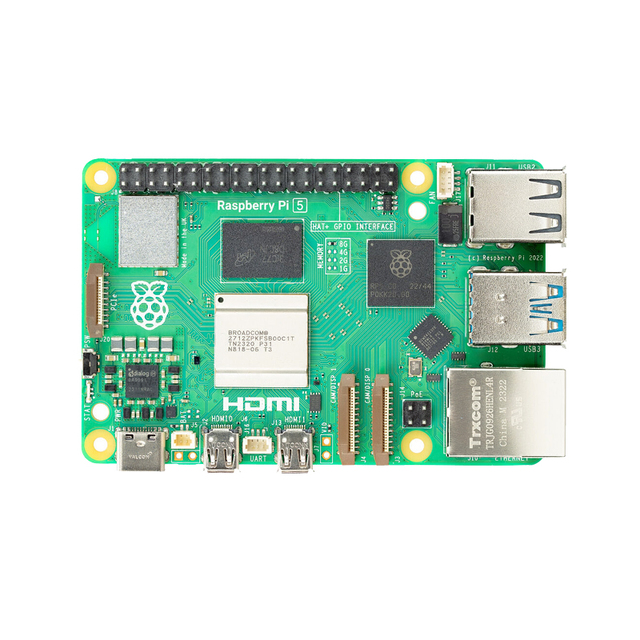

Raspberry Pi 5

De Raspberry Pi 5 gëtt vun engem 64-Bit Quad-Core Arm Cortex-A76 Prozessor mat 2,4 GHz ugedriwwen, wat eng 2-3 Mol besser CPU-Leeschtung am Verglach zum Raspberry Pi 4 bitt. Zousätzlech gouf d'Grafikleeschtung vum 800MHz Video Core VII GPU däitlech verbessert; Duebel 4Kp60 Display-Ausgang iwwer HDMI; Nieft der fortgeschrattener Kameraënnerstëtzung vum nei designten Raspberry PI Bildsignalprozessor bitt en de Benotzer eng reibungslos Desktop-Erfahrung a mécht d'Dier op fir nei Uwendungen fir industriell Clienten.

2,4 GHz Quad-Core, 64-Bit Arm Cortex-A76 CPU mat 512 KB L2 Cache an 2 MB gedeelt L3 Cache

Video Core VII GPU, Ënnerstëtzung fir Open GL ES 3.1, Vulkan 1.2

Duebel 4Kp60 HDMI@ Displayausgang mat HDR-Ënnerstëtzung

4Kp60 HEVC Decoder

LPDDR4X-4267 SDRAM (Verfügbar mat 4GB an 8GB RAM beim Start)

Duebelband 802.11ac Wi-Fi⑧

Bluetooth 5.0 / Bluetooth Low Energy (BLE)

MicroSD-Kaarteslot, ënnerstëtzt High-Speed-SDR104-Modus

Zwee USB 3.0 Ports, déi synchron Operatioun vu 5 Gbps ënnerstëtzen

2 USB 2.0 Ports

Gigabit Ethernet, PoE+ Ënnerstëtzung (separat PoE+ HAT erfuerderlech)

2 x 4-Kanal MIPI Kamera/Display Transceiver

PCIe 2.0 x1 Interface fir séier Peripheriegeräter (separat M.2 HAT oder aner Adapter erfuerderlech)

5V/5A DC Stroumversuergung, USB-C Interface, Ënnerstëtzung fir Stroumversuergung

Raspberry PI Standard 40 Nadelen

Echtzäituhr (RTC), déi vun enger externer Batterie ugedriwwe gëtt

Power-Knäppchen

-

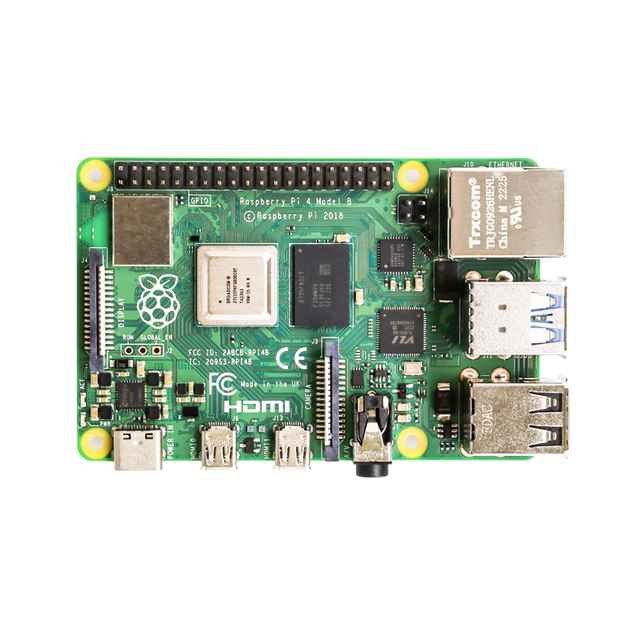

Raspberry Pi 4B

De Raspberry Pi 4B ass eng nei Ergänzung zu der Raspberry Pi-Computerfamill. D'Prozessorgeschwindegkeet ass am Verglach mat der viregter Generatioun vum Raspberry Pi 3B+ däitlech verbessert. En huet vill Multimedia, vill Späicherplatz a besser Konnektivitéit. Fir Endbenotzer bitt de Raspberry Pi 4B eng Desktop-Performance, déi mat Basis-x86PC-Systemer vergläichbar ass.

De Raspberry Pi 4B huet e 64-Bit Quad-Core Prozessor mat 1,5 GHz; Duebel Display mat 4K Opléisung bis zu 60fps Refresh; Verfügbar an dräi Speicheroptiounen: 2GB/4GB/8GB; Onboard 2,4/5,0 GHz Dual-Band WLAN a 5.0 BLE Low Energy Bluetooth; 1 Gigabit Ethernet Port; 2 USB 3.0 Ports; 2 USB 2.0 Ports; 1 5V3A Stroumversuergungsport.

-

Traverser Racing F7 Fluchsteierung 5V 9V Duebel BEC agebauten OSD F722 Fluchsteierung

Produktkategorie: Elektronesch Accessoiren fir Spillsaachen

Urspronk: Shenzhen, Guangdong

Spillkategorie: elektrescht Spillgezei

-

Traverser F4/F7 Fluchsteierung Beidou GPS M8N Kleng Positionéierung Schnellverbindung Stabilitéitsgurtkompass

Empfindlechkeet: Positionéierung, séier Verbindung, stabil

Applikatioun: Zäitreesmaschinn

Datenformat: M8N

Produktlinn: GPS

-

Zännstäbchenmaschinn F411+20A+35A Fluchsteierung elektresch Kontroll integréiert Board 2-5S AIO

Produktkategorie: Elektronesch Accessoiren fir Spillsaachen

Spillkategorie: elektrescht Spillgezei

-

Telefon

-

E-Mail

-

WhatsApp

-

Skype

-

Skype

-

Skype