1. Allgemeng Praxis

Fir den Design vun der Héichfrequenz-Leiterplatine méi vernünfteg a besser Anti-Interferenz-Performance ze maachen, sollten déi folgend Aspekter berücksichtegt ginn:

(1) Vernünfteg Auswiel vu Schichten Beim Verleeë vun Héichfrequenz-Leiterplatten am PCB-Design gëtt déi bannenzeg Fläch an der Mëtt als Stroum- a Buedemschicht benotzt, déi eng Abschirmungsroll spille kann, effektiv d'parasitär Induktivitéit reduzéiere kann, d'Längt vun de Signalleitungen verkierzt an d'Kräizinterferenz tëscht Signaler reduzéiert.

(2) Fräsmodus De Fräsmodus muss am Aklang mat 45°-Wénkeldréiung oder Boudréiung sinn, wat d'Héichfrequentsignalemissioun an d'géigesäiteg Kopplung reduzéiere kann.

(3) Kabellängt Wat méi kuerz d'Kabellängt ass, wat besser. Wat méi kuerz den Ofstand tëscht zwou Drot ass, wat besser.

(4) Zuel vun den Duerchgänge Lächer Wat manner d'Zuel vun den Duerchgänge Lächer ass, wat besser.

(5) Richtung vun der Zwëscheschichtverkabelung D'Richtung vun der Zwëscheschichtverkabelung soll vertikal sinn, dat heescht, déi iewescht Schicht ass horizontal, déi ënnescht Schicht ass vertikal, fir d'Interferenz tëscht de Signaler ze reduzéieren.

(6) Kupferbeschichtung Eng erhéicht Äerdung vun der Kupferbeschichtung kann d'Interferenz tëscht Signaler reduzéieren.

(7) D'Integratioun vun der wichteger Signalleitungsveraarbechtung kann d'Anti-Interferenzfäegkeet vum Signal däitlech verbesseren, natierlech kann och d'Integratioun vun der Interferenzquellveraarbechtung sinn, sou datt se keng aner Signaler stéiere kann.

(8)Signalkabele leeden keng Signaler a Schleifen. Leeden Signaler am Daisy-Chain-Modus.

2. Verkabelungsprioritéit

Schlësselsignallinnprioritéit: analogt klengt Signal, Héichgeschwindegkeetssignal, Auersignal a Synchroniséierungssignal an aner Schlësselsignaler Prioritéitsverdrahtung

Dicht als éischt Prinzip: Fänkt d'Verkabelung vun de komplexeste Verbindungen op der Platin un. Fänkt d'Verkabelung vun der dichtst verdrahtter Zone vun der Platin un.

Punkten déi et ze bemierken gëtt:

A. Versicht eng speziell Verdrahtungsschicht fir Schlësselsignaler wéi Auersignaler, Héichfrequenzsignaler a sensibel Signaler ze bidden, a garantéiert eng minimal Schleiffläch. Wann néideg, sollten manuell Prioritéitsverdrahtung, Abschirmung an erhéicht Sécherheetsofstänn ugeholl ginn. Séchert d'Signalqualitéit.

b. D'EMC-Ëmfeld tëscht der Leeschtungsschicht an der Äerd ass schlecht, dofir sollten Interferenzempfindlech Signaler vermeit ginn.

c. D'Netzwierk mat Ufuerderunge fir d'Impedanzkontroll soll sou wäit wéi méiglech no den Ufuerderunge fir d'Leitungslängt an d'Leitungsbreet verdraat ginn.

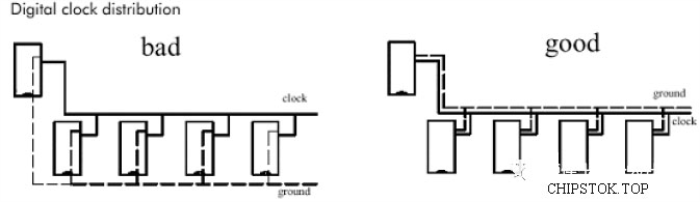

3, Auerverdrahtung

D'Auerleitung ass ee vun de gréissten Faktoren, déi den EMC beaflossen. Maacht manner Lächer an der Auerleitung, vermeit sou wäit wéi méiglech mat anere Signalleitungen ze goen, a bleift ewech vun allgemenge Signalleitungen, fir Stéierungen mat de Signalleitungen ze vermeiden. Gläichzäiteg sollt d'Stroumversuergung op der Platin vermeit ginn, fir Stéierungen tëscht der Stroumversuergung an der Auer ze vermeiden.

Wann et e speziellen Auerchip op der Platin gëtt, däerf en net ënner d'Linn goen, soll ënner dem Koffer geluecht ginn, wann néideg, kann och speziell op säi Land geluecht ginn. Fir vill Chip-Referenzkristalloszillatoren, sollten dës Kristalloszillatoren net ënner der Linn sinn, fir Kofferisolatioun ze leeën.

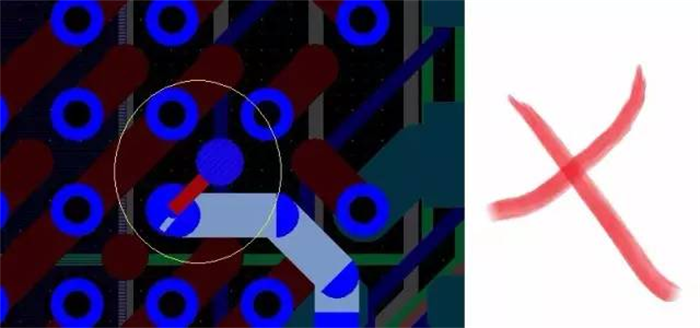

4. Linn am rechte Wénkel

Rechtwénkelkabelung ass am Allgemengen noutwendeg fir d'Situatioun bei der PCB-Verkabelung ze vermeiden, an ass bal ee vun de Standarden fir d'Moosse vun der Qualitéit vun der Verkabelung ginn. Wéi vill Impakt huet also rechtwénkelkabelung op d'Signaliwwerdroung? Am Prinzip féiert rechtwénkel Verkabelung dozou, datt d'Leitungsbreet vun der Iwwerdroungsleitung ännert, wat zu enger Impedanzdiskontinuitéit féiert. Tatsächlech kann net nëmmen rechtwénkel Verkabelung, mee och spitzwénkel Verkabelung Impedanzännerungen verursaachen.

Den Afloss vum rechtwénkelege Routing op d'Signal spigelt sech haaptsächlech an dräi Aspekter erëm:

Éischtens kann d'Eck gläichwäerteg mat der kapazitiver Belaaschtung op der Transmissiounsleitung sinn, wouduerch d'Opstigzäit verlangsamt gëtt;

Zweetens, Impedanzdiskontinuitéit wäert d'Signalreflexioun verursaachen;

Drëttens, EMI, deen vun der rechtwénkeger Spëtzt produzéiert gëtt.

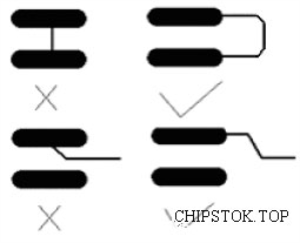

5. Spitzen Wénkel

(1) Bei Héichfrequenzstroum, wann den Dréipunkt vum Drot e rechte Wénkel oder souguer e spitze Wénkel weist, no bei der Eck, sinn d'Magnéitfluxdicht an d'elektrescht Feldintensitéit relativ héich, d'Stralung wäert staark elektromagnetesch Wellen hunn, an d'Induktivitéit hei wäert relativ grouss sinn, den induktive Wénkel wäert méi grouss sinn wéi de stumpfe Wénkel oder de gerundete Wénkel.

(2) Fir d'Busverdrahtung vum digitale Circuit ass den Eck vun der Verdrahtung stomp oder gerundet, d'Fläch vun der Verdrahtung ass relativ kleng. Ënner der selwechter Bedingung vum Linnenofstand ass den gesamten Linnenofstand 0,3 Mol manner Breet wéi déi rechtwénkleg Wendung.

6. Differenziell Routing

Cf. Differenzialverdrahtung an Impedanzanpassung

Differenzialsignaler ginn ëmmer méi dacks beim Design vun Héichgeschwindegkeetsschaltunge benotzt, well déi wichtegst Signaler a Schaltunge ëmmer eng Differenzialstruktur benotzen. Definitioun: Einfach ausgedréckt heescht dat, datt den Treiber zwee gläichwäerteg, invertéierend Signaler schéckt, an den Empfänger bestëmmt, ob den logeschen Zoustand "0" oder "1" ass, andeems en den Ënnerscheed tëscht den zwou Spannungen vergläicht. Dat Puer, dat den Differenzialsignal dréit, gëtt Differenzialrouting genannt.

Am Verglach mat normaler Single-Ended-Signalrouting huet den Differentialsignal déi offensichtlechst Virdeeler an de folgenden dräi Aspekter:

a. Staark Anti-Interferenz-Fäegkeet, well d'Kopplung tëscht den zwou Differenzialleitungen ganz gutt ass, ass et bal gläichzäiteg mat den zwou Leitungen verbonnen, wann et Rauschen vun dobausse gëtt, an den Empfänger këmmert sech nëmmen ëm den Ënnerscheed tëscht den zwou Signaler, sou datt de Common-Mode-Rauschen vun dobausse komplett ausgeschalt ka ginn.

b. kann EMI effektiv hemmen. Ähnlech, well d'Polaritéit vun zwee Signaler entgéintgesat ass, kënnen déi elektromagnetesch Felder, déi vun hinnen ausgestraalt ginn, sech géigesäiteg ausgläichen. Wat méi enk d'Kopplung ass, wat manner elektromagnetesch Energie un d'Äussewelt fräigesat gëtt.

c. Präzis Zäitpositioun. Well d'Schaltännerunge vun Differenzialsignaler op der Kräizung vun zwéi Signaler leien, ass den Impakt vun der Technologie an der Temperatur, am Géigesaz zu normale Single-End-Signaler, déi op héich an niddreg Schwellspannung vertrauen, kleng, wat d'Feeler am Timing reduzéiere kann an ass besser fir Schaltunge mat Signaler mat gerénger Amplitude geegent. LVDS (Low Voltage Differential Signaling), déi de Moment populär ass, bezitt sech op dës Differenzialsignaltechnologie mat klenger Amplitude.

Fir PCB-Ingenieuren ass dat Wichtegst sécherzestellen, datt d'Virdeeler vum Differentialrouting voll am tatsächleche Routing ausgenotzt kënne ginn. Vläicht soulaang de Kontakt mat de Layout-Leit déi allgemeng Ufuerderunge vum Differentialrouting versteet, dat heescht "gläich Längt, gläich Distanz".

Déi gläich Längt ass dofir do, fir sécherzestellen, datt déi zwee Differentialsignaler ëmmer eng géigesätzlech Polaritéit behalen an d'Common-Mode-Komponent ze reduzéieren. D'Äquivalentdistanz ass haaptsächlech dozou do, sécherzestellen, datt d'Differenzimpedanz konsequent ass an d'Reflexioun reduzéiert gëtt. "Sou no wéi méiglech" ass heiansdo eng Viraussetzung fir Differentialrouting.

7. Schlaanglinn

Eng Schlaangelinn ass eng Zort Layout, déi dacks am Layout benotzt gëtt. Säin Haaptzweck ass et, d'Verzögerung unzepassen an d'Ufuerderunge vum Systemtiming-Design ze erfëllen. Dat Éischt, wat Designer musse realiséieren, ass datt schlaangefërmeg Drot d'Signalqualitéit zerstéiere kënnen an d'Transmissiounsverzögerung änneren, an dofir sollten se beim Verkabelen vermeit ginn. Fir awer am aktuellen Design eng genuch Haltzäit vu Signaler ze garantéieren oder den Zäitoffset tëscht der selwechter Grupp vu Signaler ze reduzéieren, ass et dacks néideg, bewosst ze wikkelen.

Punkten déi et ze bemierken gëtt:

Puer vun Differenzsignalleitungen, meeschtens parallel Leitungen, sou wéineg wéi méiglech duerch d'Lach, musse gestanzt ginn, et sollten zwou Leitungen zesummen sinn, fir eng Impedanzanpassung z'erreechen.

Eng Grupp vu Bussen mat de selwechten Attributer soll sou wäit wéi méiglech niewentenee verluecht ginn, fir eng gläich Längt z'erreechen. D'Lach, dat vum Patchpad aus féiert, ass sou wäit wéi méiglech vum Pad ewech.

Zäitpunkt vun der Verëffentlechung: 05. Juli 2023