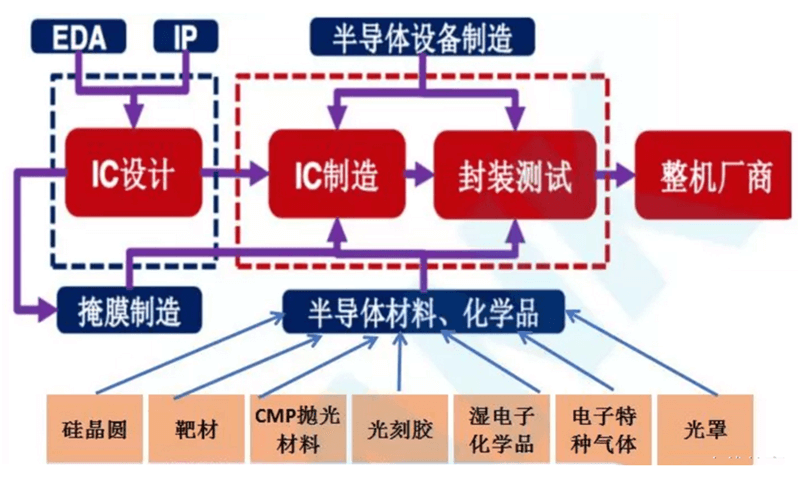

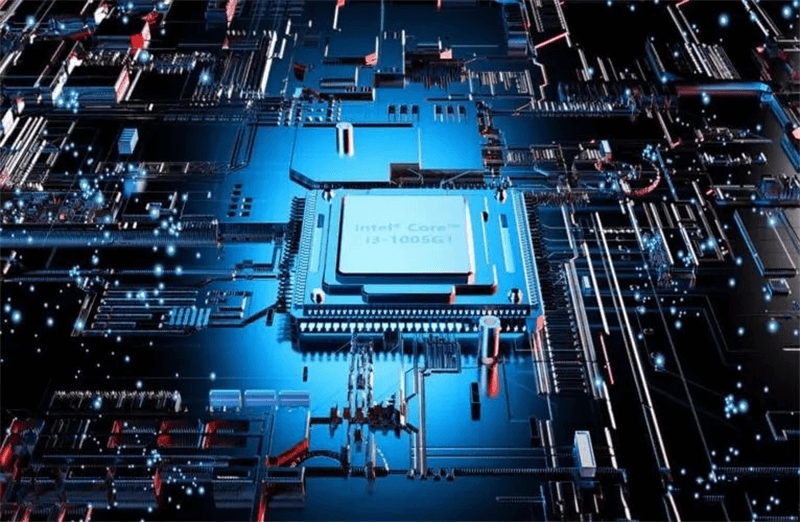

Aus professioneller Siicht ass de Produktiounsprozess vun engem Chip extrem komplizéiert an zäitopwänneg. Wéi och ëmmer, vun der kompletter Industriekette vun IC aus ass en haaptsächlech a véier Deeler opgedeelt: IC-Design → IC-Herstellung → Verpackung → Testen.

Chipproduktiounsprozess:

1. Chip-Design

De Chip ass e Produkt mat klengem Volumen, awer extrem héijer Präzisioun. Fir e Chip ze maachen, ass den Design den éischten Deel. Den Design erfuerdert d'Hëllef vum Chipdesign, deen fir d'Veraarbechtung mat Hëllef vum EDA-Tool a verschiddenen IP-Kären erfuerderlech ass.

Chipproduktiounsprozess:

1. Chip-Design

De Chip ass e Produkt mat klengem Volumen, awer extrem héijer Präzisioun. Fir e Chip ze maachen, ass den Design den éischten Deel. Den Design erfuerdert d'Hëllef vum Chipdesign, deen fir d'Veraarbechtung mat Hëllef vum EDA-Tool a verschiddenen IP-Kären erfuerderlech ass.

3. Silikon-Lifting

Nodeems de Silizium getrennt ass, ginn déi reschtlech Materialien opginn. Pure Silizium huet no verschiddene Schrëtt d'Qualitéit vun der Hallefleederherstellung erreecht. Dëst ass de sougenannten elektronesche Silizium.

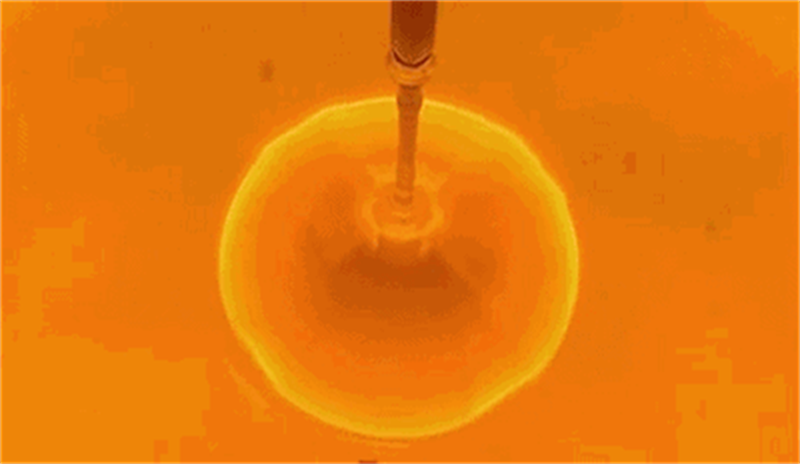

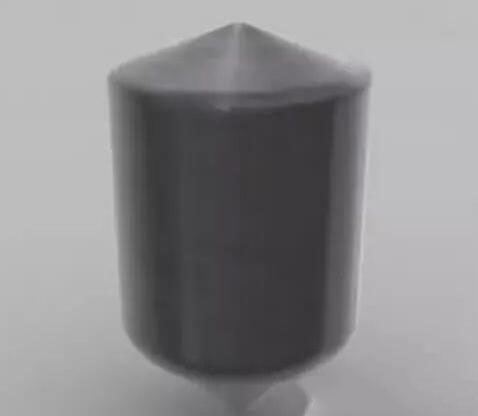

4. Silizium-Gossbarren

Nom Reinigung soll de Silizium a Siliziumbarren gegoss ginn. En Eenzelkristall vun engem elektronesche Silizium weit no der Gegossung a Baren ongeféier 100 kg, an d'Reinheet vum Silizium erreecht 99,9999%.

5. Dateiveraarbechtung

Nodeems de Siliziumbarre gegoss ass, muss de ganze Siliziumbarre a Stécker geschnidden ginn, dat ass de Wafer, deen mir allgemeng Wafer nennen, deen ganz dënn ass. Duerno gëtt de Wafer poléiert bis en perfekt ass, an d'Uewerfläch sou glat wéi e Spigel ass.

Den Duerchmiesser vu Siliziumwaferen ass 8 Zoll (200 mm) an 12 Zoll (300 mm). Wat méi grouss den Duerchmiesser ass, wat méi niddreg d'Käschte vun engem eenzege Chip sinn, awer wat méi schwéier d'Veraarbechtung ass.

5. Dateiveraarbechtung

Nodeems de Siliziumbarre gegoss ass, muss de ganze Siliziumbarre a Stécker geschnidden ginn, dat ass de Wafer, deen mir allgemeng Wafer nennen, deen ganz dënn ass. Duerno gëtt de Wafer poléiert bis en perfekt ass, an d'Uewerfläch sou glat wéi e Spigel ass.

Den Duerchmiesser vu Siliziumwaferen ass 8 Zoll (200 mm) an 12 Zoll (300 mm). Wat méi grouss den Duerchmiesser ass, wat méi niddreg d'Käschte vun engem eenzege Chip sinn, awer wat méi schwéier d'Veraarbechtung ass.

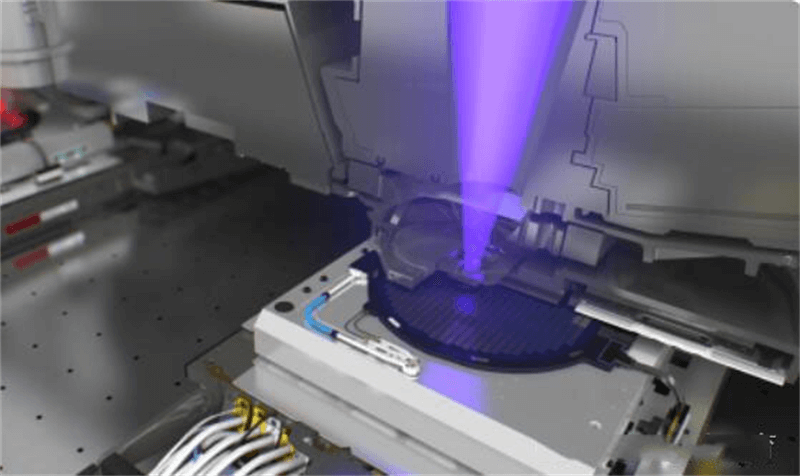

7. Sonnendäischtert an Ioneninjektioun

Als éischt ass et néideg, Siliziumoxid a Siliziumnitrid, déi baussent dem Photoresist ausgesat sinn, ze korrodéieren, an eng Schicht Silizium auszesetzen, fir tëscht dem Kristallröhrchen ze isoléieren, an dann d'Ätztechnologie ze benotzen, fir dat ënnescht Silizium fräizeleeën. Dann gëtt de Bor oder de Phosphor an d'Siliziumstruktur injizéiert, dann de Koffer opfëllen, fir mat aneren Transistoren ze verbannen, an dann eng weider Schicht Klebstoff dropzedroen, fir eng Strukturschicht ze bilden. Am Allgemengen enthält e Chip Dosende vu Schichten, wéi dicht verflochte Stroossen.

7. Sonnendäischtert an Ioneninjektioun

Als éischt ass et néideg, Siliziumoxid a Siliziumnitrid, déi baussent dem Photoresist ausgesat sinn, ze korrodéieren, an eng Schicht Silizium auszesetzen, fir tëscht dem Kristallröhrchen ze isoléieren, an dann d'Ätztechnologie ze benotzen, fir dat ënnescht Silizium fräizeleeën. Dann gëtt de Bor oder de Phosphor an d'Siliziumstruktur injizéiert, dann de Koffer opfëllen, fir mat aneren Transistoren ze verbannen, an dann eng weider Schicht Klebstoff dropzedroen, fir eng Strukturschicht ze bilden. Am Allgemengen enthält e Chip Dosende vu Schichten, wéi dicht verflochte Stroossen.

Zäitpunkt vun der Verëffentlechung: 08. Juli 2023