Aféierung vun der Kontrollklass-Chip

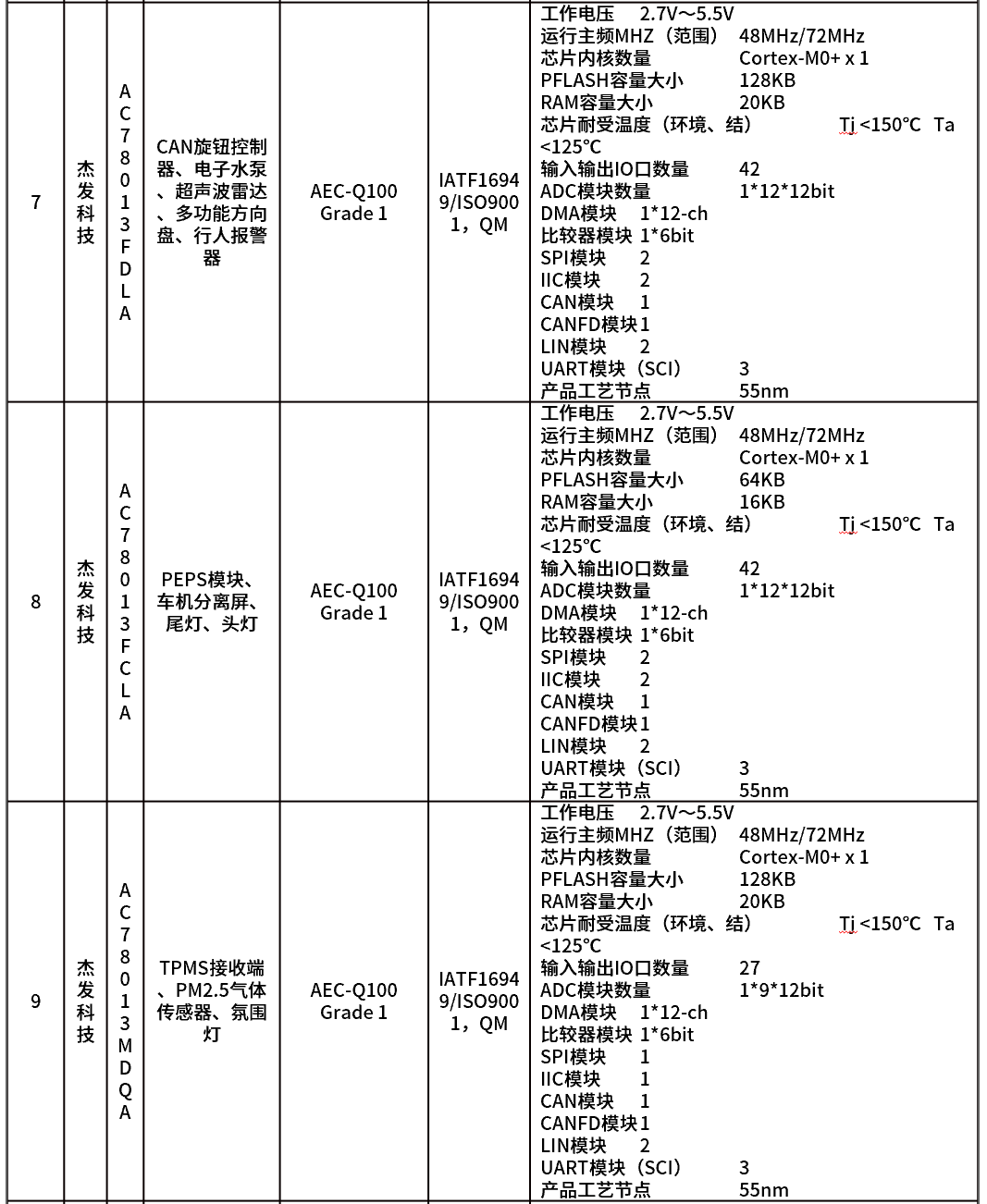

De Kontrollchip bezitt sech haaptsächlech op d'MCU (Microcontroller Unit), dat heescht de Mikrocontroller, och bekannt als Single-Chip, deen d'CPU-Frequenz an d'Spezifikatioune entspriechend reduzéiere soll, an de Speicher, den Timer, d'A/D-Konversioun, d'Auer, den I/O-Port an d'Seriellkommunikatioun an aner funktionell Moduler an Interfaces sinn op engem eenzege Chip integréiert. Duerch d'Ëmsetzung vun der Terminalkontrollfunktioun huet en d'Virdeeler vun héijer Leeschtung, niddregem Energieverbrauch, programméierbarer a grousser Flexibilitéit.

MCU-Diagramm vum Niveau vum Gefier

D'Automobilindustrie ass e ganz wichtegen Uwendungsberäich vun MCU, laut Donnéeë vun IC Insights huet déi global MCU-Applikatioun an der Automobilelektronik am Joer 2019 ongeféier 33% ausgemaach. D'Zuel vun den MCUS, déi vun all Auto an High-End-Modeller benotzt ginn, ass no bei 100, vu Fuercomputer, LCD-Instrumenter bis hin zu Motoren, Chassis, grouss a kleng Komponenten am Auto, déi MCU-Steierung brauchen.

An den Ufankszäiten goufen 8-Bit- a 16-Bit-MCUS haaptsächlech an Autoen benotzt, awer mat der kontinuéierlecher Verbesserung vun der Elektroniséierung an der Intelligenz am Automobilberäich klëmmt och d'Zuel an d'Qualitéit vun den erfuerderleche MCUS. De Moment huet den Undeel vun 32-Bit-MCUS an den MCUS am Automobilberäich ongeféier 60% erreecht, vun deenen den ARM Cortex-Serie-Kernel, wéinst senge niddrege Käschten an exzellenter Energiesteierung, déi Mainstream-Wiel vun den Hiersteller vun MCU-Systemer am Automobilberäich ass.

Zu den Haaptparameter vun engem Automotive-MCU gehéieren d'Betribsspannung, d'Betribsfrequenz, d'Flash- a RAM-Kapazitéit, d'Nummer vum Timermodul an dem Kanal, d'Nummer vum ADC-Modul an dem Kanal, den Typ an d'Nummer vum serielle Kommunikatiounsinterface, d'Nummer vum Input- an Output-I/O-Port, d'Betribstemperatur, d'Verpackungsform an de funktionelle Sécherheetsniveau.

No CPU-Bits opgedeelt, kann den Automobil-MCUS haaptsächlech an 8-Bit, 16-Bit an 32-Bit opgedeelt ginn. Mat der Prozessupgrade falen d'Käschte vum 32-Bit-MCUS weider, an et ass elo Mainstream ginn, an et ersetzt lues a lues d'Applikatiounen a Mäert, déi fréier vun 8/16-Bit-MCUS dominéiert goufen.

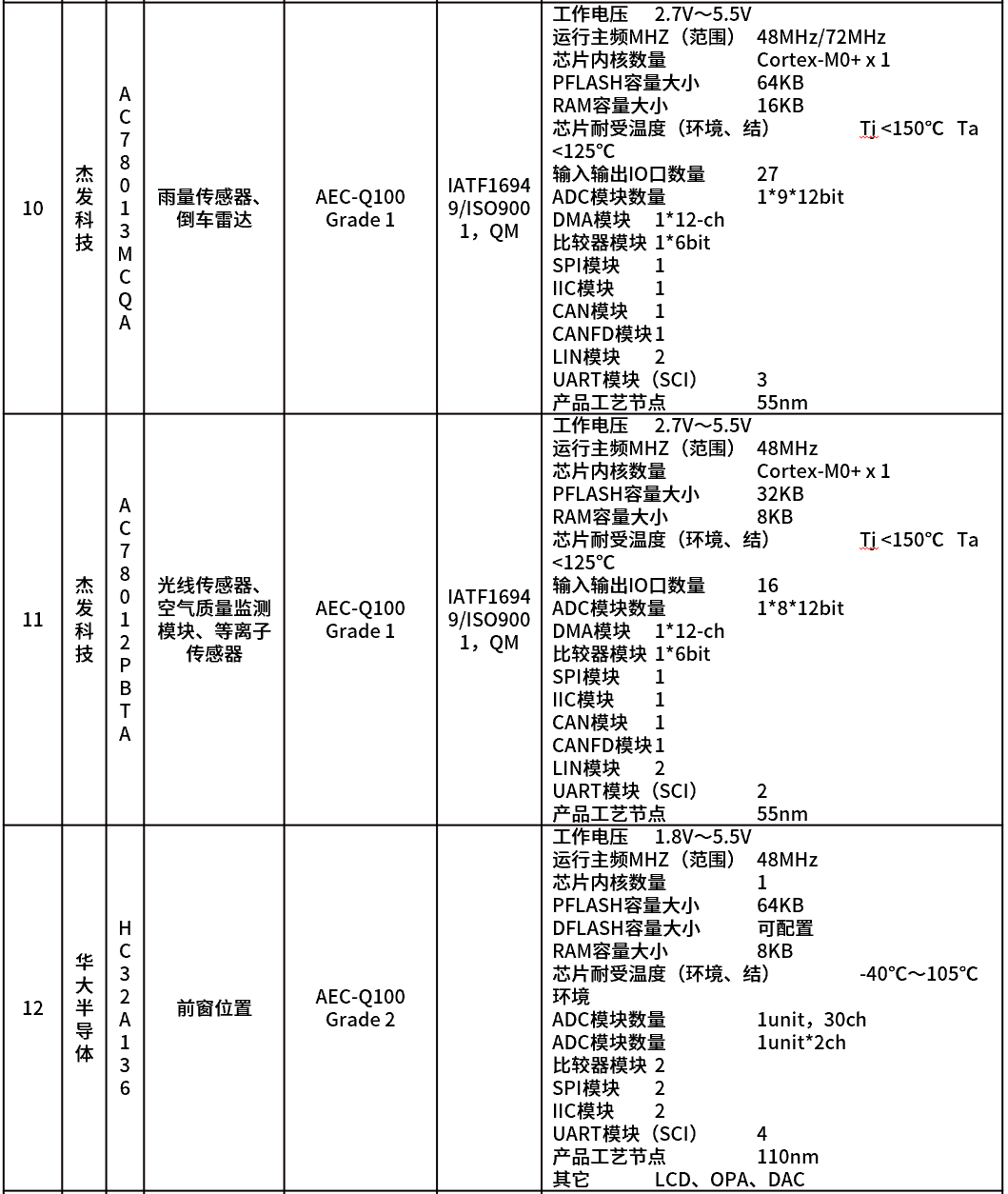

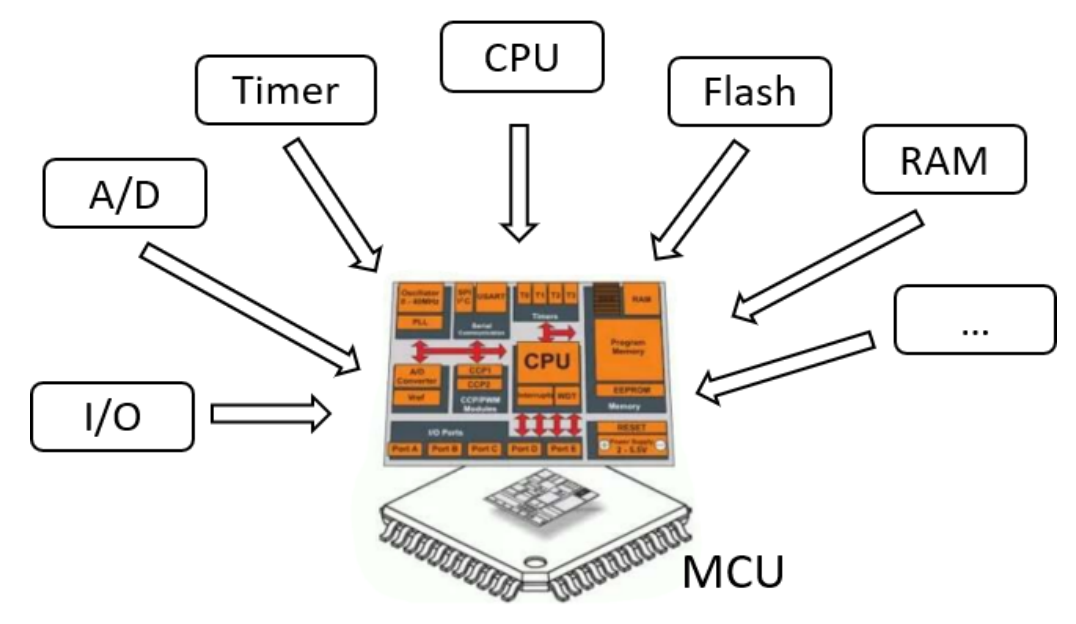

Wann een no dem Uwendungsberäich opgedeelt gëtt, kann den Automotive-MCU an de Karosserieberäich, de Leeschtungsberäich, de Chassisberäich, de Cockpitberäich an den intelligenten Undriffberäich opgedeelt ginn. Fir de Cockpitberäich an den intelligenten Undriffberäich brauch den MCU eng héich Rechenleistung an extern Kommunikatiounsinterfaces mat héijer Geschwindegkeet, wéi CAN FD an Ethernet. De Karosserieberäich erfuerdert och eng grouss Zuel vun externen Kommunikatiounsinterfaces, awer de Rechenleistungsbedarf vum MCU ass relativ niddreg, während de Leeschtungsberäich an de Chassisberäich méi héich Betribstemperaturen a funktionell Sécherheetsniveauen erfuerderen.

Chassis Domain Kontrollchip

Den Chassisberäich bezitt sech op d'Fueren vun engem Gefier a besteet aus dem Transmissiounssystem, dem Fuersystem, dem Lenksystem an dem Bremssystem. Et besteet aus fënnef Ënnersystemer, nämlech Lenkung, Bremsung, Schaltung, Gaspedal an Ophiewesystem. Mat der Entwécklung vun der Autointelligenz sinn d'Wahrnehmungserkennung, d'Entscheedungsplanung an d'Kontrollausféierung vun intelligenten Gefierer déi zentral Systemer vum Chassisberäich. Steering-by-Wire an Drive-by-Wire sinn déi zentral Komponenten fir den exekutive Beräich vum automatesche Fueren.

(1) Ufuerderunge fir d'Aarbecht

D'ECU am Chassis-Beräich benotzt eng héich performant, skalierbar funktionell Sécherheetsplattform a ënnerstëtzt Sensorclustering a Multiachs-Inertialsensoren. Baséierend op dësem Applikatiounsszenario ginn déi folgend Ufuerderunge fir d'MCU am Chassis-Beräich virgeschloen:

· Héich Frequenz an héich Rechenleistungsufuerderungen, d'Haaptfrequenz ass net manner wéi 200 MHz an d'Rechenleistung ass net manner wéi 300 DMIPS

· De Flash-Späicherplatz ass net manner wéi 2 MB, mat enger physescher Code-Flash- a Daten-Flash-Partition;

· RAM net manner wéi 512 KB;

· Héich Ufuerderunge fir de funktionelle Sécherheetsniveau, kënnen den ASIL-D Niveau erreechen;

· Ënnerstëtzung vun engem 12-Bit Präzisiouns-ADC;

· Ënnerstëtzung vun 32-Bit héich Präzisioun, héich Synchroniséierungstimer;

· Ënnerstëtzung vu Multikanal-CAN-FD;

· Ënnerstëtzung vun net manner wéi 100M Ethernet;

· Zouverlässegkeet net méi niddereg wéi AEC-Q100 Grad 1;

· Ënnerstëtzung fir Online-Upgrades (OTA);

· Ënnerstëtzung vun der Firmware-Verifizéierungsfunktioun (nationalen geheimen Algorithmus);

(2) Leeschtungsufuerderungen

· Kärdeel:

I. Kärfrequenz: dat heescht d'Taktfrequenz beim Betrib vum Kernel, déi benotzt gëtt fir d'Geschwindegkeet vun der digitaler Pulssignaloszillatioun vum Kernel duerzestellen, an d'Haaptfrequenz kann net direkt d'Berechnungsgeschwindegkeet vum Kernel representéieren. D'Betribsgeschwindegkeet vum Kernel hänkt och mat der Kernel-Pipeline, dem Cache, dem Instruktiounsset, etc. zesummen.

II. Rechenleistung: DMIPS kann normalerweis fir d'Evaluatioun benotzt ginn. DMIPS ass eng Eenheet, déi déi relativ Leeschtung vum integréierte Benchmarkprogramm vun der MCU moosst, wann et getest gëtt.

· Speicherparameter:

I. Code-Speicher: Speicher, deen zum Späichere vu Code benotzt gëtt;

II. Datenspeicher: Speicher, deen zur Späicherung vun Daten benotzt gëtt;

III.RAM: Speicher, deen benotzt gëtt fir temporär Daten a Code ze späicheren.

· Kommunikatiounsbus: inklusiv Autospezialbus a konventionelle Kommunikatiounsbus;

· Héichpräzis Peripheriegeräter;

· Betribstemperatur;

(3) Industriell Muster

Well d'elektresch an elektronesch Architektur, déi vun ënnerschiddlechen Autoshersteller benotzt gëtt, variéiert, wäerten och d'Komponentufuerderunge fir de Chassisberäich variéieren. Wéinst der ënnerschiddlecher Konfiguratioun vu verschiddene Modeller vun der selwechter Autofabrik wäert d'ECU-Auswiel vum Chassisberäich ënnerschiddlech sinn. Dës Ënnerscheeder féieren zu ënnerschiddlechen MCU-Ufuerderunge fir de Chassisberäich. Zum Beispill benotzt den Honda Accord dräi MCU-Chips am Chassisberäich, an den Audi Q7 benotzt ongeféier 11 MCU-Chips am Chassisberäich. Am Joer 2021 gouf ongeféier 10 Millioune chinesesch Persounewagen produzéiert, dovun ass déi duerchschnëttlech Nofro fir MCUS am Chassisberäich vu Vëloen 5, an de Gesamtmaart huet ongeféier 50 Milliounen erreecht. Déi Haaptliwweranten vun MCUS am Chassisberäich sinn Infineon, NXP, Renesas, Microchip, TI an ST. Dës fënnef international Hallefleeder-Hiersteller maachen méi wéi 99% vum Maart fir MCUS am Chassisberäich aus.

(4) Industriebarrièren

Aus engem wichtegen technesche Standpunkt aus sinn d'Komponente vum Chassisberäich wéi EPS, EPB, ESC enk mat der Liewenssécherheet vum Chauffer verbonnen, dofir ass de funktionelle Sécherheetsniveau vun den MCU am Chassisberäich ganz héich, am Fong Ufuerderunge vum ASIL-D-Niveau. Dëse funktionelle Sécherheetsniveau vun MCU ass a China eidel. Nieft dem funktionelle Sécherheetsniveau hunn d'Applikatiounsszenarie vu Chassiskomponenten ganz héich Ufuerderungen un d'MCU-Frequenz, d'Rechenleistung, d'Speicherkapazitéit, d'Peripherieperformance, d'Peripheriegenauegkeet an aner Aspekter. D'MCU am Chassisberäich huet eng ganz héich Industriebarrière geformt, déi vun den inlännesche MCU-Hiersteller muss erausgefuerdert a gebrach ginn.

Wat d'Liwwerkette ugeet, ginn, wéinst den Ufuerderunge vun héijer Frequenz a vun héijer Rechenleistung fir de Kontrollchip vun de Chassis-Domänkomponenten, relativ héich Ufuerderunge fir de Prozess an d'Verfahre vun der Waferproduktioun gestallt. Am Moment schéngt et, datt op d'mannst e 55nm-Prozess noutwendeg ass, fir d'Frequenzufuerderunge vun der MCU iwwer 200MHz ze erfëllen. An dëser Hisiicht ass déi national MCU-Produktiounslinn nach net komplett an huet nach net de Masseproduktiounsniveau erreecht. International Hallefleederhersteller hunn am Fong den IDM-Modell ugeholl, wat d'Wafergiewerien ugeet, hunn de Moment nëmmen TSMC, UMC a GF déi entspriechend Fäegkeeten. National Chiphersteller sinn all Fabless-Firmen, an et gëtt Erausfuerderungen a gewësse Risiken an der Waferproduktioun an der Kapazitéitssécherung.

A Kärcomputer-Szenarien, wéi zum Beispill autonomt Fueren, sinn traditionell Allzweck-CPUs schwéier un d'KI-Computerufuerderungen unzepassen, well se manner Rechenleistung hunn. KI-Chips wéi GPUs, FPgas an ASics hunn eng exzellent Leeschtung um Edge an an der Cloud mat hiren eegene Charakteristiken a gi wäit verbreet benotzt. Aus der Perspektiv vun den Technologietrends wäert d'GPU kuerzfristeg nach ëmmer den dominanten KI-Chip sinn, a laangfristeg ass den ASIC déi ultimativ Richtung. Aus der Perspektiv vun de Maarttrends wäert déi global Nofro fir KI-Chips e schnelle Wuesstemsmoment behalen, a Cloud- an Edge-Chips hunn e gréissert Wuesstemspotenzial, an et gëtt erwaart, datt de Maartwuesstem an den nächste fënnef Joer bei bal 50% läit. Och wann d'Basis vun der nationaler Chiptechnologie schwaach ass, schaaft de schnelle Volumen vun der Nofro fir KI-Chips mat der schneller Landung vun KI-Applikatiounen Méiglechkeeten fir den Technologie- a Fäegkeetswuesstem vu lokale Chip-Entreprisen. Autonomt Fueren huet streng Ufuerderungen u Rechenleistung, Verzögerung a Zouverlässegkeet. Am Moment gi meeschtens GPU+FPGA-Léisunge benotzt. Mat der Stabilitéit vun Algorithmen an dem Datenorientéierten gëtt erwaart, datt ASics Maartplaz gewannen.

Vill Plaz gëtt um CPU-Chip fir d'Branchprediktioun an d'Optimiséierung gebraucht, wouduerch verschidde Staaten gespuert ginn, fir d'Latenz vum Task Switching ze reduzéieren. Dëst mécht en och méi gëeegent fir Logiksteierung, seriellen Operatiounen an allgemeng Datenoperatiounen. Zum Beispill GPU an CPU: Am Verglach mat der CPU benotzt d'GPU eng grouss Zuel vu Recheneenheeten an eng laang Pipeline, nëmmen eng ganz einfach Kontrolllogik an eliminéiert de Cache. D'CPU hëlt net nëmmen vill Plaz vum Cache an, mä huet och eng komplex Kontrolllogik a vill Optimiséierungsschaltkreesser, wouduerch d'Rechenleistung nëmmen e klengen Deel ass.

Power Domain Kontrollchip

De Power Domain Controller ass eng intelligent Undriffsmanagementeenheet. Mat CAN/FLEXRAY fir d'Getriebsmanagement, d'Batteriemanagement, d'Iwwerwaachung vun der Alternatorreguléierung z'erreechen, gëtt en haaptsächlech fir d'Optimiséierung an d'Steierung vum Undriff benotzt, wärend souwuel elektresch intelligent Fehlerdiagnos, intelligent Energiespuerung, Buskommunikatioun an aner Funktiounen benotzt ginn.

(1) Ufuerderunge fir d'Aarbecht

De Power Domain Control MCU kann grouss Uwendungen am Beräich vun der Energieversuergung, wéi zum Beispill BMS, mat de folgende Viraussetzungen ënnerstëtzen:

· Héich Haaptfrequenz, Haaptfrequenz 600MHz~800MHz

· RAM 4 MB

· Héich Ufuerderunge fir de funktionelle Sécherheetsniveau, kënnen den ASIL-D Niveau erreechen;

· Ënnerstëtzung vu Multikanal-CAN-FD;

· Ënnerstëtzung fir 2G Ethernet;

· Zouverlässegkeet net méi niddereg wéi AEC-Q100 Grad 1;

· Ënnerstëtzung vun der Firmware-Verifizéierungsfunktioun (nationalen geheimen Algorithmus);

(2) Leeschtungsufuerderungen

Héich Leeschtung: Dëst Produkt integréiert den ARM Cortex R5 Dual-Core Lock-Step CPU an 4MB On-Chip SRAM fir déi wuessend Rechenleistung an d'Speicherufuerderunge vun Automobilapplikatiounen z'ënnerstëtzen. ARM Cortex-R5F CPU bis zu 800MHz. Héich Sécherheet: De Zouverlässegkeetsstandard AEC-Q100 fir Gefierspezifikatiounen erreecht Grad 1, an den ISO26262 funktionelle Sécherheetsniveau erreecht ASIL D. Den Dual-Core Lock-Step CPU kann eng Diagnoseofdeckung vu bis zu 99% erreechen. Den agebauten Informatiounssécherheetsmodul integréiert en echte Zoufallszuelgenerator, AES, RSA, ECC, SHA an Hardwarebeschleuniger, déi de relevante Standarde vun der staatlecher a geschäftlecher Sécherheet entspriechen. D'Integratioun vun dësen Informatiounssécherheetsfunktiounen kann d'Bedierfnesser vun Applikatiounen wéi sécheren Start, sécher Kommunikatioun, sécher Firmware-Updates an Upgrades erfëllen.

Chip fir d'Kontroll vun der Kierperfläch

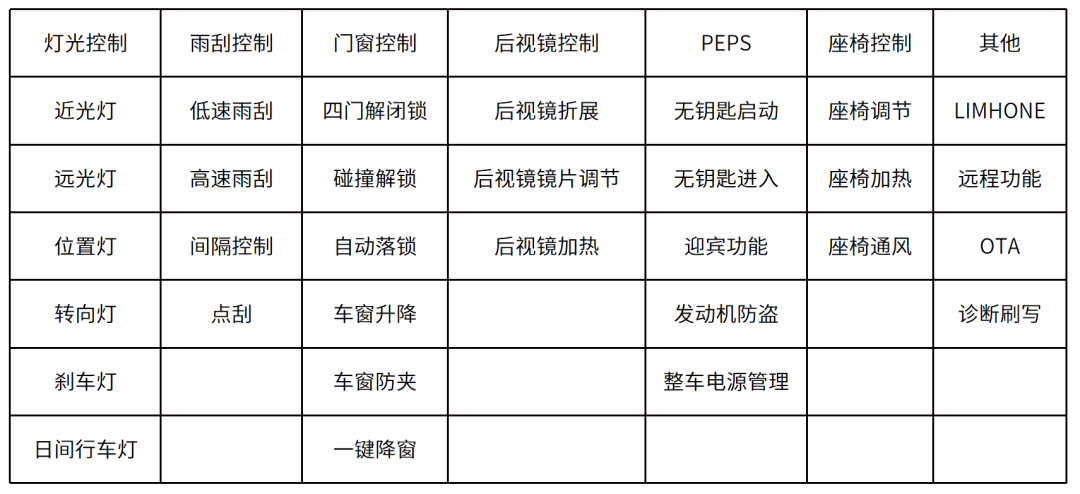

De Karosserieberäich ass haaptsächlech verantwortlech fir d'Steierung vu verschiddene Funktiounen vun der Karosserie. Mat der Entwécklung vum Gefier gëtt de Karosserieberäichcontroller och ëmmer méi benotzt. Fir d'Käschte vum Controller ze reduzéieren an d'Gewiicht vum Gefier ze reduzéieren, muss d'Integratioun all funktionell Geräter, vum viischten Deel, dem mëttleren Deel vum Auto an dem hënneschten Deel vum Auto, wéi d'hënnescht Bremsluucht, d'hënnescht Positiounsluucht, d'hënnescht Dierverriegelung, a souguer d'Duebelstützstang, an engem komplette Controller integréiert ginn.

De Kierperflächencontroller integréiert am Allgemengen BCM, PEPS, TPMS, Gateway an aner Funktiounen, kann awer och d'Sëtzverstellung, d'Réckspigelkontroll, d'Klimaanlagkontroll an aner Funktiounen erweideren, wat eng ëmfaassend an eenheetlech Gestioun vun all Aktuatoren erméiglecht, an eng raisonnabel an effektiv Allokatioun vun de Systemressourcen. D'Funktioune vun engem Kierperflächencontroller si villfälteg, wéi hei ënnendrënner gewisen, awer si sinn net limitéiert op déi, déi hei opgezielt sinn.

(1) Ufuerderunge fir d'Aarbecht

Déi Haaptufuerderunge vun der Automobilelektronik fir MCU-Steierchips sinn eng besser Stabilitéit, Zouverlässegkeet, Sécherheet, Echtzäit- an aner technesch Charakteristiken, souwéi eng méi héich Rechenleistung a Späicherkapazitéit, a méi niddreg Ufuerderungen un de Stroumverbrauchsindex. De Karosseriecontroller ass lues a lues vun enger dezentraliséierter funktioneller Asaz op e grousse Controller iwwergaangen, deen all d'Basisantriebs vun der Karosserieelektronik, Schlësselfunktiounen, Luuchten, Dieren, Fënsteren, etc. integréiert. Den Design vum Karosseriecontrollersystem integréiert Beliichtung, Scheibewëscherwäsch, zentral Steierungsdierverriegelungen, Fënsteren an aner Kontrollen, intelligent PEPS-Tasten, Energiemanagement, etc. Souwéi Gateway CAN, erweiterbar CANFD a FLEXRAY, LIN-Netzwierk, Ethernet-Interface a Modulentwécklung an -designtechnologie.

Am Allgemengen spigelen sech d'Aarbechtsufuerderunge vun den uewe genannten Kontrollfunktioune fir den MCU-Haaptkontrollchip am Karosserieberäich haaptsächlech an den Aspekter vun der Berechnungs- a Veraarbechtungsleistung, der funktioneller Integratioun, der Kommunikatiounsschnittstell an der Zouverlässegkeet erëm. Wat déi spezifesch Ufuerderunge ugeet, wéinst de funktionellen Ënnerscheeder an de verschiddene funktionellen Uwendungsszenarien am Karosserieberäich, wéi elektresch Fënsteren, automatesch Sëtzer, elektresch Heckklappe an aner Karosserieapplikatiounen, gëtt et ëmmer nach héich effizient Motorsteierungsbedürfnisser. Sou Karosserieapplikatioune verlaangen datt den MCU den elektronesche Kontrollalgorithmus vum FOC an aner Funktiounen integréiert. Zousätzlech hunn ënnerschiddlech Uwendungsszenarien am Karosserieberäich ënnerschiddlech Ufuerderungen un d'Schnittstellkonfiguratioun vum Chip. Dofir ass et normalerweis néideg, den MCU vum Karosserieberäich no de funktionellen an de Leeschtungsufuerderunge vum spezifeschen Uwendungsszenario ze wielen, an op dëser Basis d'Produktkäschteleistung, d'Liwwerkapazitéit an den technesche Service an aner Faktoren ëmfaassend ze moossen.

(2) Leeschtungsufuerderungen

Déi wichtegst Referenzindikatoren vum Kierperberäichkontroll-MCU-Chip sinn wéi follegt:

Leeschtung: ARM Cortex-M4F@ 144MHz, 180DMIPS, agebauten 8KB Instruktiouns-Cache-Cache, Ënnerstëtzung fir d'Ausféierung vun der Flash-Beschleunigungseenheet mam Programm 0 Waarden.

Verschlësselte Späicher mat grousser Kapazitéit: bis zu 512K Bytes eFlash, Ënnerstëtzung fir verschlësselte Späicherung, Partitiounsverwaltung an Datenschutz, Ënnerstëtzung fir ECC-Verifizéierung, 100.000 Läschzäiten, 10 Joer Datenspeicherung; 144K Bytes SRAM, Ënnerstëtzung fir Hardwareparitéit.

Integréiert räich Kommunikatiounsinterfaces: Ënnerstëtzung vu Multi-Channel GPIO, USART, UART, SPI, QSPI, I2C, SDIO, USB2.0, CAN 2.0B, EMAC, DVP an aner Interfaces.

Integréierten Héichleistungssimulator: Ënnerstëtzung fir en 12-Bit 5Msps Héichgeschwindegkeets-ADC, en onofhängege Schinn-zu-Schinn-Operatiounsverstärker, en analoge Héichgeschwindegkeetskomparator, en 12-Bit 1Msps DAC; Ënnerstëtzung fir extern Input-onofhängeg Referenzspannungsquell, kapazitiv Touchtasten mat méi Kanäl; Héichgeschwindegkeets-DMA-Controller.

Ënnerstëtzung vun interner RC oder externer Kristalluhr-Input, héich Zouverlässegkeets-Reset.

Agebaute Kalibrierung RTC Echtzäituhr, Ënnerstëtzung fir Schaltjoers-Eewegkalenner, Alarmereignisser, periodescht Weckstart.

Ënnerstëtzung fir héichpräzis Timing-Zähler.

Sécherheetsfeatures op Hardware-Niveau: Hardwarebeschleunigungsmotor fir d'Verschlësselungsalgorithmus, Ënnerstëtzung vun den Algorithmen AES, DES, TDES, SHA1/224/256, SM1, SM3, SM4, SM7, MD5; Verschlësselung vu Flash-Späicher, Gestioun vu Multi-User-Partitionen (MMU), TRNG-Zoufallszuelengenerator, CRC16/32-Betrib; Ënnerstëtzung vum Schreifschutz (WRP), Ënnerstëtzung vum Liesschutz (RDP)-Niveauen (L0/L1/L2); Ënnerstëtzung vum Sécherheetsstart, Eroflueden vu Programmverschlësselung, Sécherheetsupdates.

Ënnerstëtzung fir d'Iwwerwaachung vun Auerfehler an d'Iwwerwaachung géint Ofbroch.

96-Bit UID an 128-Bit UCID.

Héich zouverlässeg Aarbechtsëmfeld: 1,8V ~ 3,6V/-40℃ ~ 105℃.

(3) Industriell Muster

Den elektronesche System fir d'Karosseriefläch ass nach ëmmer an der fréier Phas vum Wuesstem, souwuel fir auslännesch wéi och fir national Entreprisen. Auslännesch Entreprisen wéi BCM, PEPS, Dieren a Fënsteren, Sëtzcontroller an aner Eenzelfunktiounsprodukter hunn eng déif technesch Akkumulatioun, während déi grouss auslännesch Firmen eng breet Ofdeckung vu Produktlinnen hunn, wat d'Grondlag fir Systemintegratiounsprodukter leeën. National Entreprisen hunn gewësse Virdeeler bei der Uwendung vun der neier Energiekarosserie fir Gefierer. Zum Beispill BYD: am neien Energiegefier vu BYD ass d'Karosseriefläch an e lénksen a rietse Beräich opgedeelt, an d'Produkt vun der Systemintegratioun gëtt nei arrangéiert a definéiert. Wat d'Karosserieflächekontrollchips ugeet, sinn awer nach ëmmer Infineon, NXP, Renesas, Microchip, ST an aner international Chiphersteller den Haaptliwwerant vu MCU, an national Chiphersteller hunn de Moment e klenge Maartundeel.

(4) Industriebarrièren

Aus der Perspektiv vun der Kommunikatioun gëtt et den Evolutiounsprozess vun der traditioneller Architektur - Hybridarchitektur - der definitiver Gefiercomputerplattform. D'Ännerung vun der Kommunikatiounsgeschwindegkeet, souwéi d'Präisreduktioun vun der Basisrechenleistung mat héijer funktioneller Sécherheet sinn de Schlëssel, an et ass méiglech, d'Kompatibilitéit vu verschiddene Funktiounen um elektronesche Niveau vum Basiscontroller an Zukunft schrëttweis ëmzesetzen. Zum Beispill kann de Karosserieberäichcontroller traditionell BCM-, PEPS- a Ripple-Anti-Pinch-Funktiounen integréieren. Relativ gesinn sinn déi technesch Barrièren vum Karosserieberäichkontrollchip méi niddreg wéi dee vum Leeschtungsberäich, dem Cockpitberäich usw., an et gëtt erwaart, datt déi national Chips d'Féierung bei engem groussen Duerchbroch am Karosserieberäich iwwerhuelen an d'Substitutioun am Land schrëttweis ëmsetzen. An de leschte Joren huet den nationale MCU am Maart fir Front- a Heckmontage vum Karosserieberäich e ganz gudden Entwécklungsdynamik erlieft.

Cockpit-Kontrollchip

Elektrifizéierung, Intelligenz a Vernetzung hunn d'Entwécklung vun der elektronescher an elektrescher Architektur am Automobilberäich a Richtung vun der Domainkontroll beschleunegt, an de Cockpit entwéckelt sech och séier vum Audio- a Video-Entertainment-System vum Gefier zum intelligenten Cockpit. De Cockpit huet eng Mënsch-Computer-Interaktiounsschnittstell, awer egal ob et sech ëm dat fréiert Infotainment-System oder den aktuellen intelligenten Cockpit handelt, zousätzlech zu engem staarke SOC mat Rechengeschwindegkeet brauch en och eng Echtzäit-MCU fir d'Dateninteraktioun mam Gefier ze handhaben. Déi graduell Populariséierung vu softwaredefinéierte Gefierer, OTA an Autosar am intelligenten Cockpit mécht d'Ufuerderunge fir MCU-Ressourcen am Cockpit ëmmer méi héich. Speziell spigelt sech an der wuessender Nofro no FLASH- a RAM-Kapazitéit erëm, an d'Nofro no PIN-Zuel klëmmt och, méi komplex Funktiounen erfuerderen méi staark Programmausféierungskapazitéiten, awer hunn och eng méi räich Bus-Schnittstell.

(1) Ufuerderunge fir d'Aarbecht

De Mikrocontroller am Kabinnberäich realiséiert haaptsächlech System-Energiemanagement, Power-On-Timing-Management, Netzwierkmanagement, Diagnos, Interaktioun mat Gefierdaten, Schlëssel-, Hannergrondbeliichtung-Management, Audio DSP/FM-Modulmanagement, Systemzäitmanagement an aner Funktiounen.

Ufuerderunge fir d'Ressourcen vum MCU:

· D'Haaptfrequenz an d'Rechenleistung hunn bestëmmt Ufuerderungen, d'Haaptfrequenz ass net manner wéi 100MHz an d'Rechenleistung ass net manner wéi 200DMIPS;

· De Flash-Späicherplatz ass net manner wéi 1 MB, mat enger physescher Partition vum Code-Flash an der Daten-Flash;

· RAM net manner wéi 128KB;

· Héich Ufuerderunge fir de funktionelle Sécherheetsniveau, kënnen den ASIL-B-Niveau erreechen;

· Ënnerstëtzung fir Multikanal-ADC;

· Ënnerstëtzung vu Multikanal-CAN-FD;

· Gefierreglement Klass AEC-Q100 Klass 1;

· Ënnerstëtzung fir Online-Upgrades (OTA), Flash-Ënnerstëtzung fir Dual Bank;

· En Informatiounsverschlësselungsmotor mat engem SHE/HSM-Liichtniveau a méi ass noutwendeg fir e séchere Start z'ënnerstëtzen;

· D'Zuel vun de PIN-Coden ass net manner wéi 100;

(2) Leeschtungsufuerderungen

IO ënnerstëtzt Breetspannungsstroumversuergung (5,5 V ~ 2,7 V), den IO-Port ënnerstëtzt d'Benotzung vun Iwwerspannung;

Vill Signalingaben schwanken jee no der Spannung vun der Batterie vum Stroumversuergungsapparat, an et kann Iwwerspannung optrieden. Iwwerspannung kann d'Systemstabilitéit a Zouverlässegkeet verbesseren.

Erënnerungsliewen:

De Liewenszyklus vum Auto ass méi wéi 10 Joer, dofir mussen de Programmspeicher an den Datenspeicher vum Auto-MCU eng méi laang Liewensdauer hunn. De Programmspeicher an den Datenspeicher mussen getrennt physikalesch Partitionen hunn, an de Programmspeicher muss manner dacks geläscht ginn, also Ausdauer > 10K, während den Datenspeicher méi dacks geläscht muss ginn, dofir muss en méi dacks geläscht ginn. Kuckt Iech den Datenblitzindikator un: Ausdauer > 100K, 15 Joer (< 1K). 10 Joer (< 100K).

Kommunikatiounsbus-Interface;

D'Buskommunikatiounsbelaaschtung um Gefier gëtt ëmmer méi héich, sou datt den traditionellen CAN-CAN den Ufuerderunge vun der Kommunikatioun net méi gerecht gëtt, den Ufuerderunge vum Héichgeschwindegkeets-CAN-FD-Bus gëtt ëmmer méi héich, an d'Ënnerstëtzung vu CAN-FD ass lues a lues zum MCU-Standard ginn.

(3) Industriell Muster

Am Moment ass den Undeel vun den nationale Smart-Cabin-MCU nach ëmmer ganz niddreg, an d'Haaptliwweranten sinn nach ëmmer NXP, Renesas, Infineon, ST, Microchip an aner international MCU-Hiersteller. Eng Rei national MCU-Hiersteller sinn am Layout, d'Maartleistung bleift ofzewaarden.

(4) Industriebarrièren

Den Niveau vun der Reguléierung an dem funktionelle Sécherheetsniveau fir intelligent Kabinneween ass relativ net ze héich, haaptsächlech wéinst der Akkumulatioun vum Know-how an dem Besoin fir kontinuéierlech Produktiteratioun a Verbesserung. Gläichzäiteg, well et net vill MCU-Produktiounslinnen an den nationale Fabriken gëtt, ass de Prozess relativ rückstänneg, et dauert eng Zäit fir déi national Produktiounsversuergungskette z'erreechen, et kann och méi héich Käschten ginn, an den Drock op Konkurrenz mat internationale Produzenten ass méi grouss.

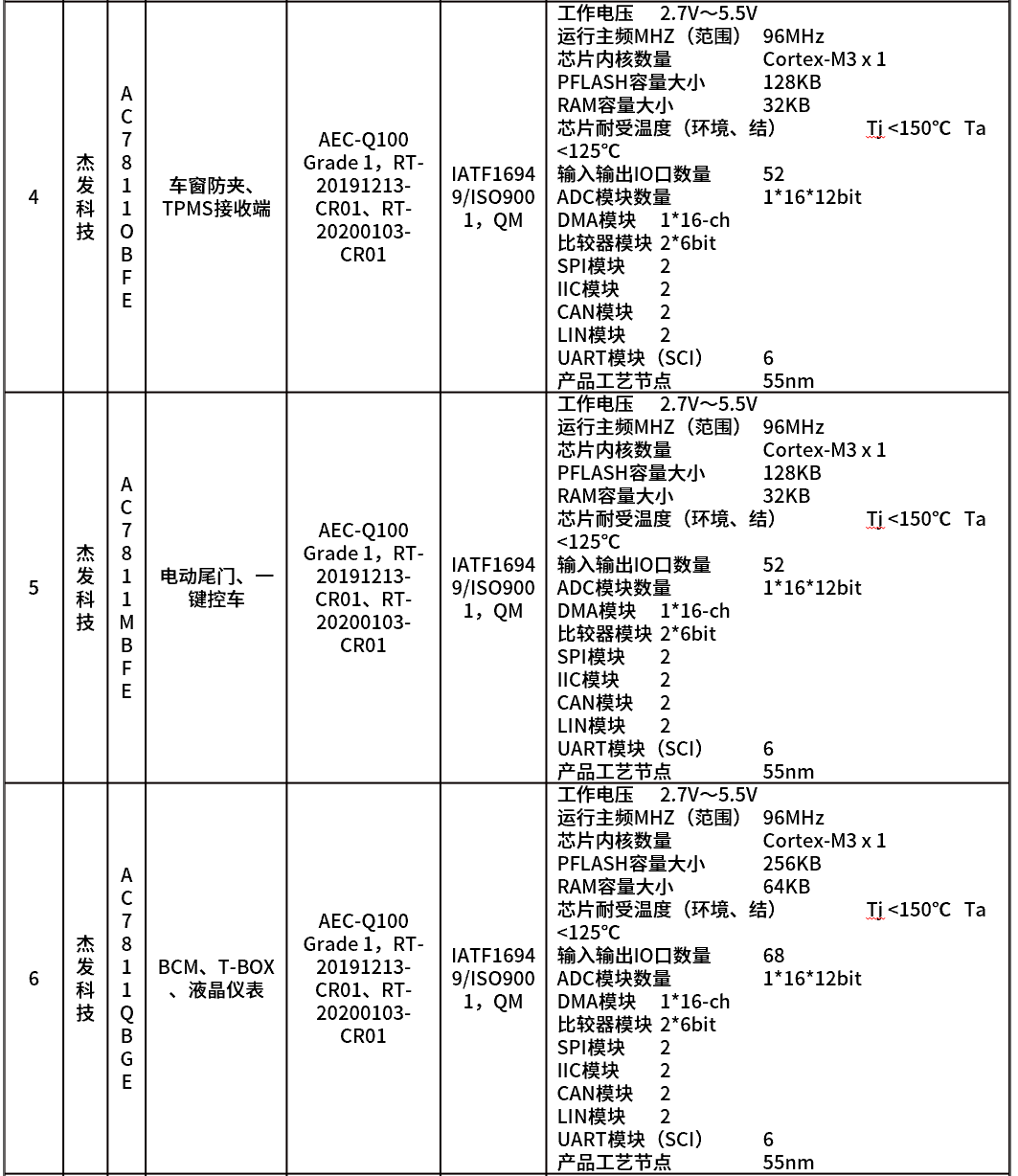

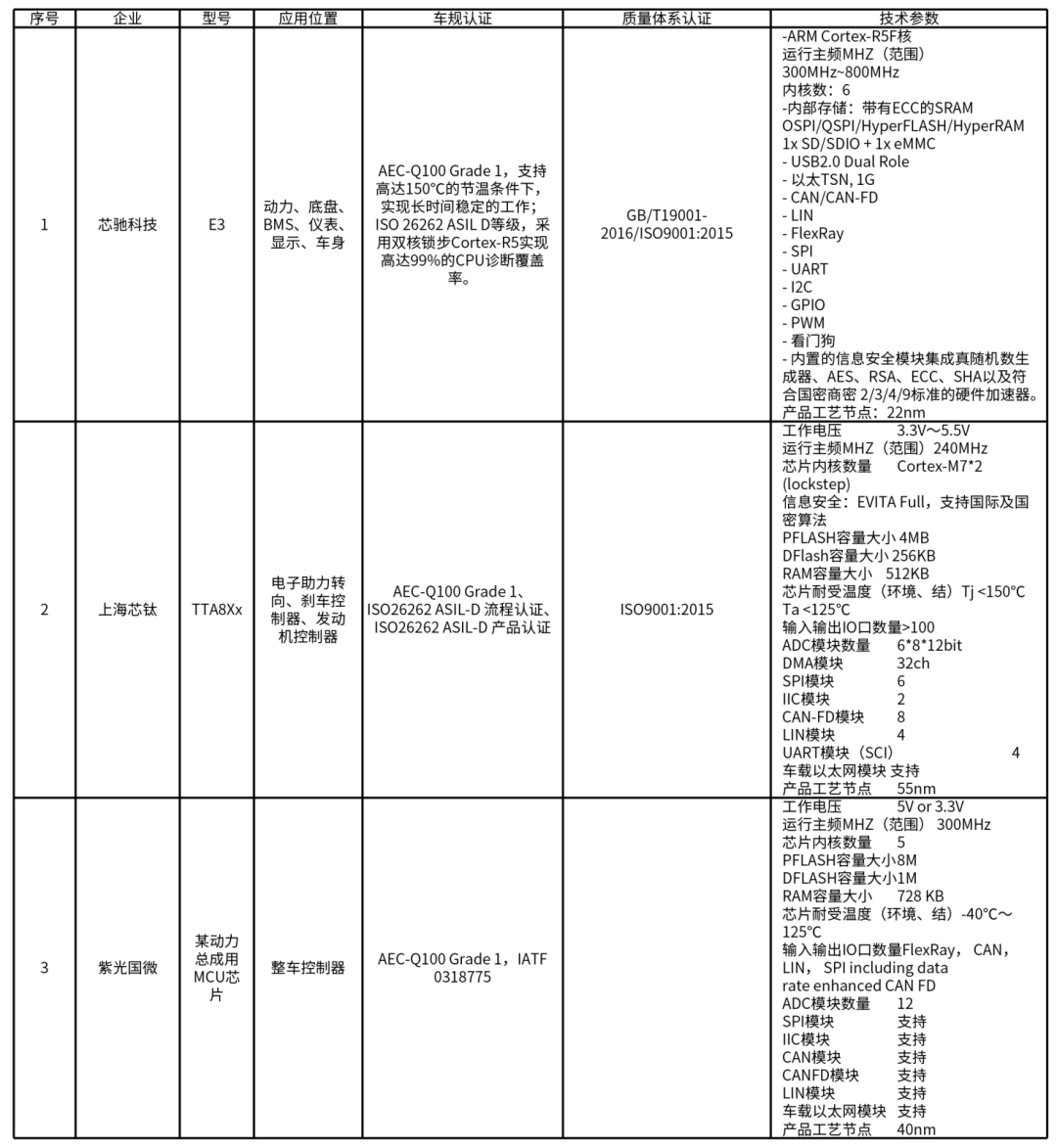

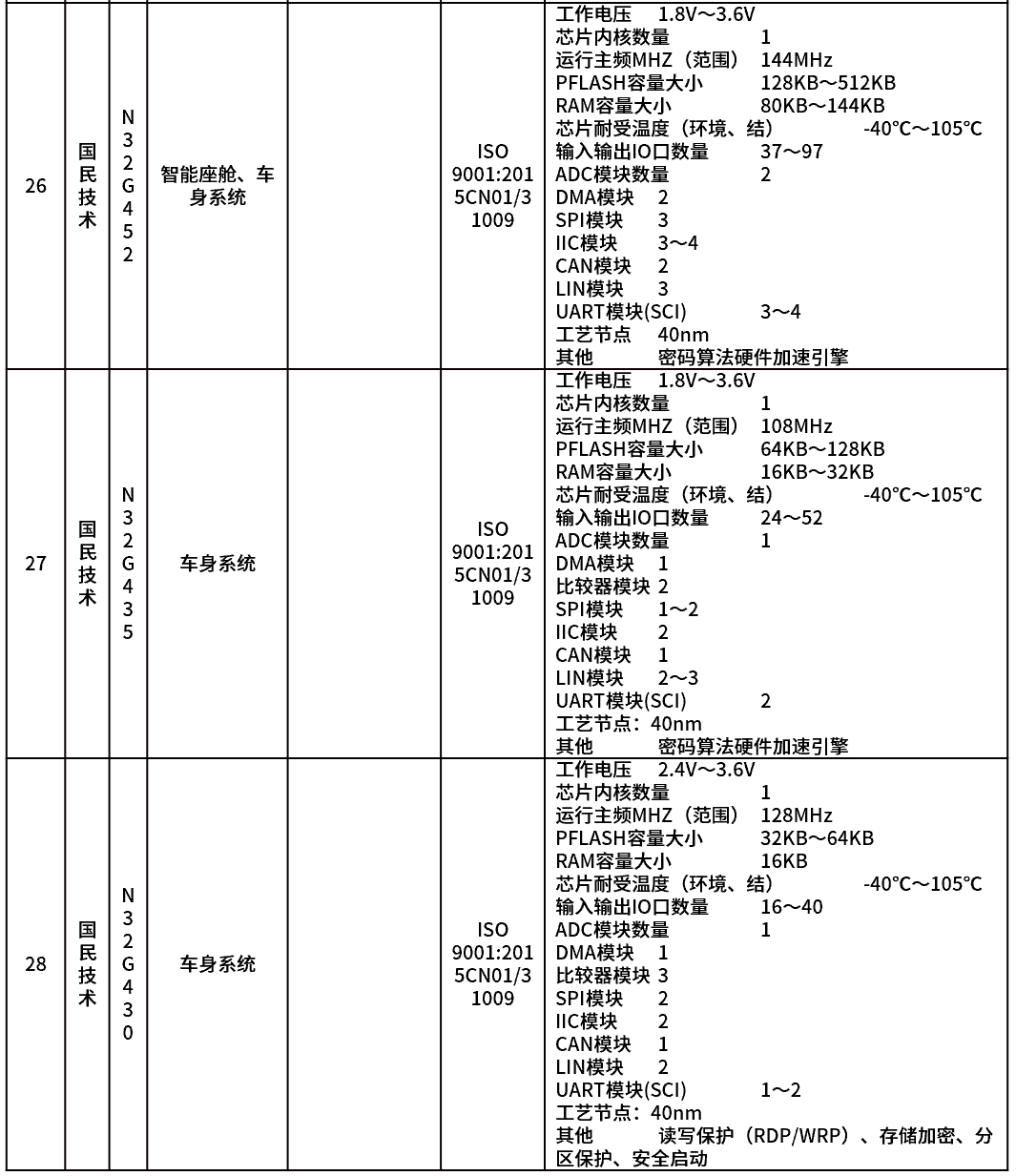

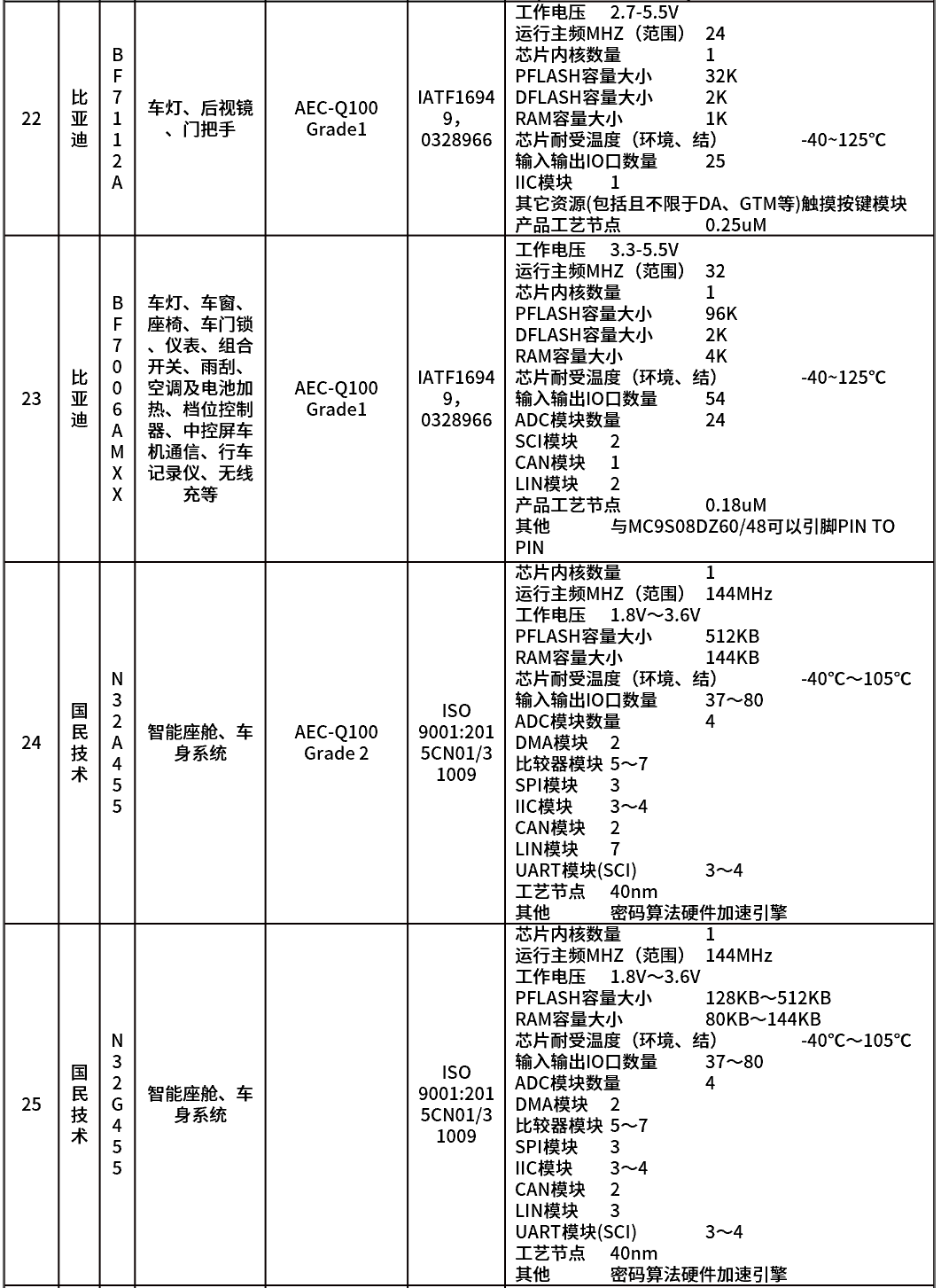

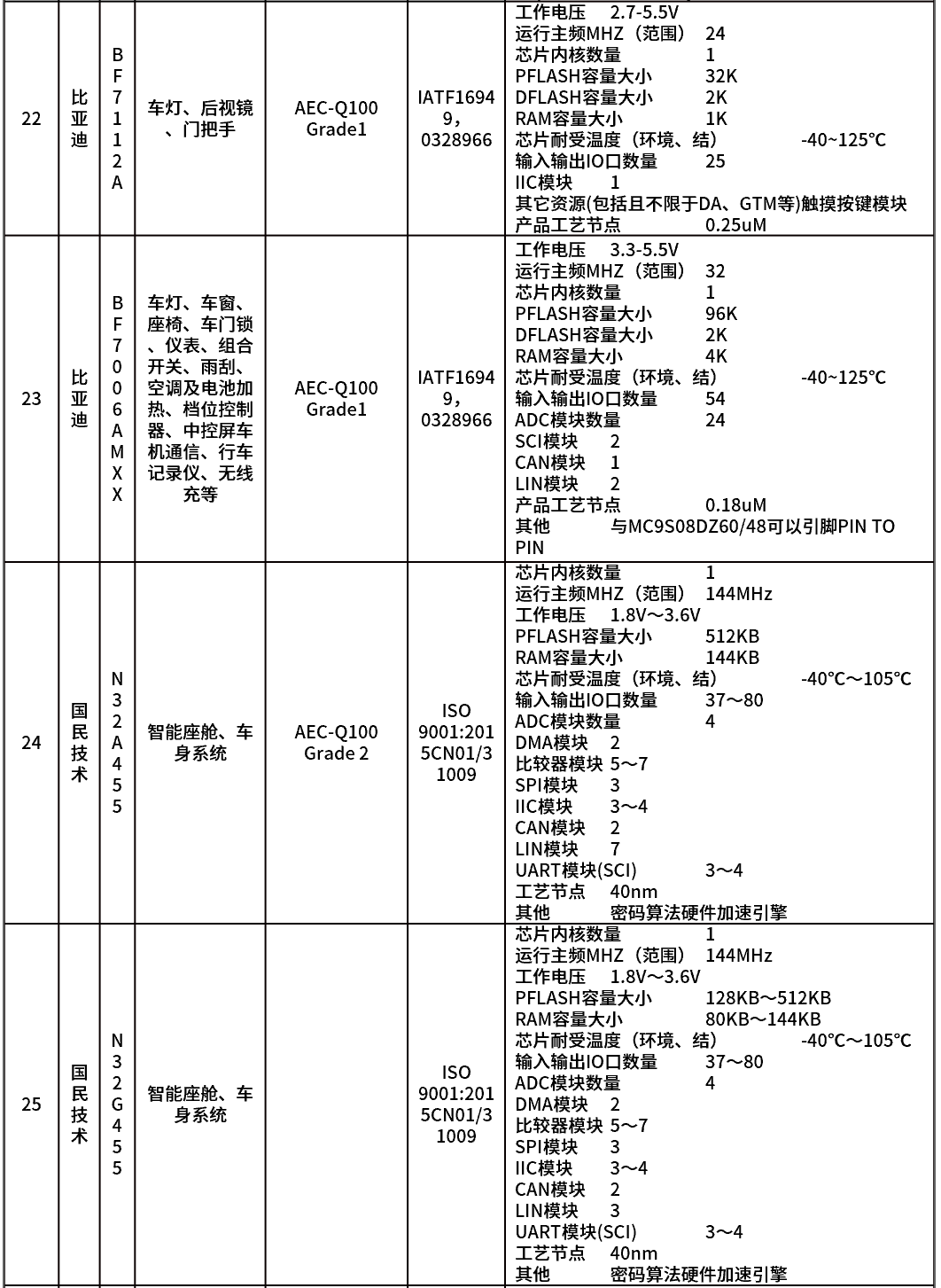

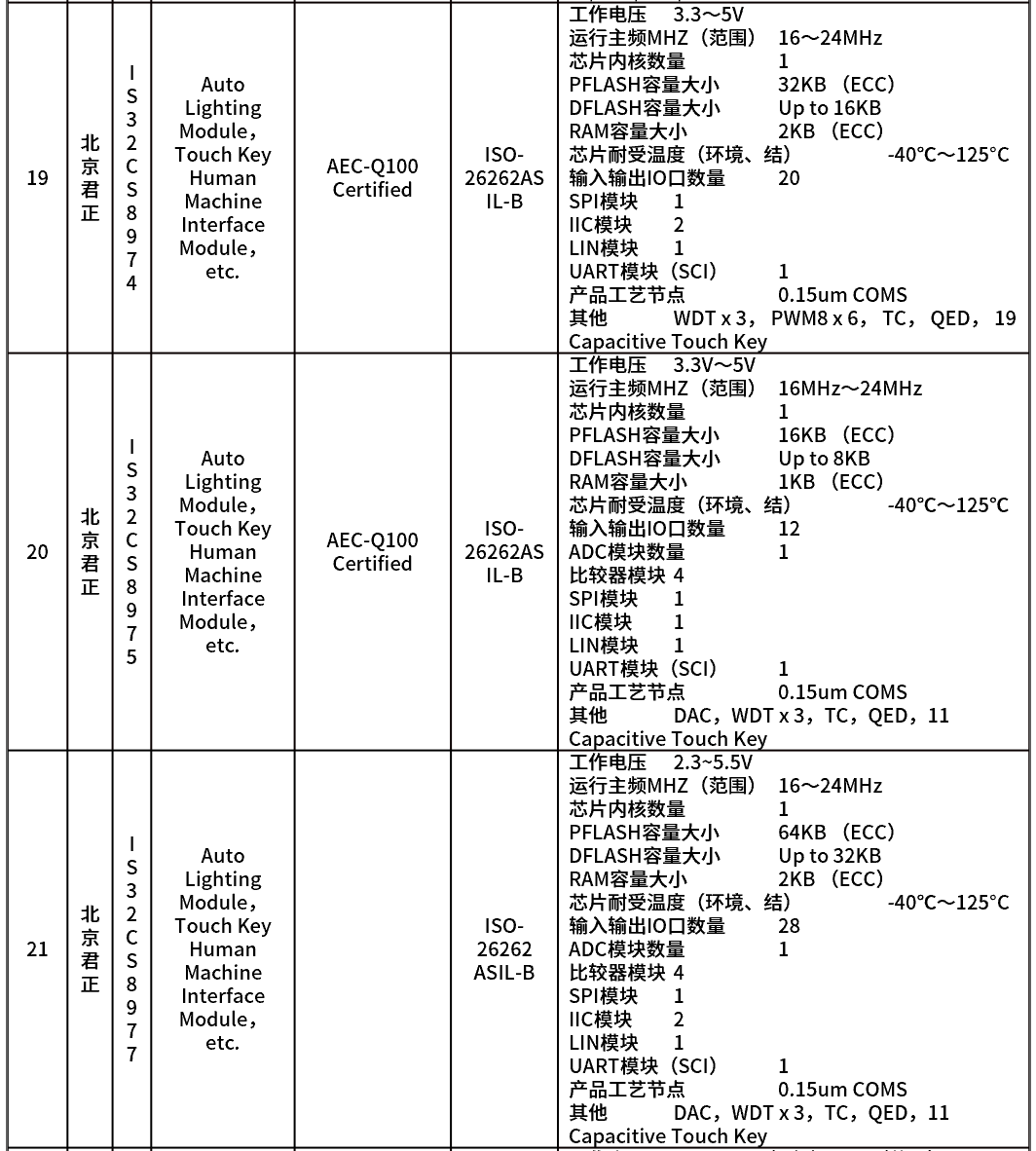

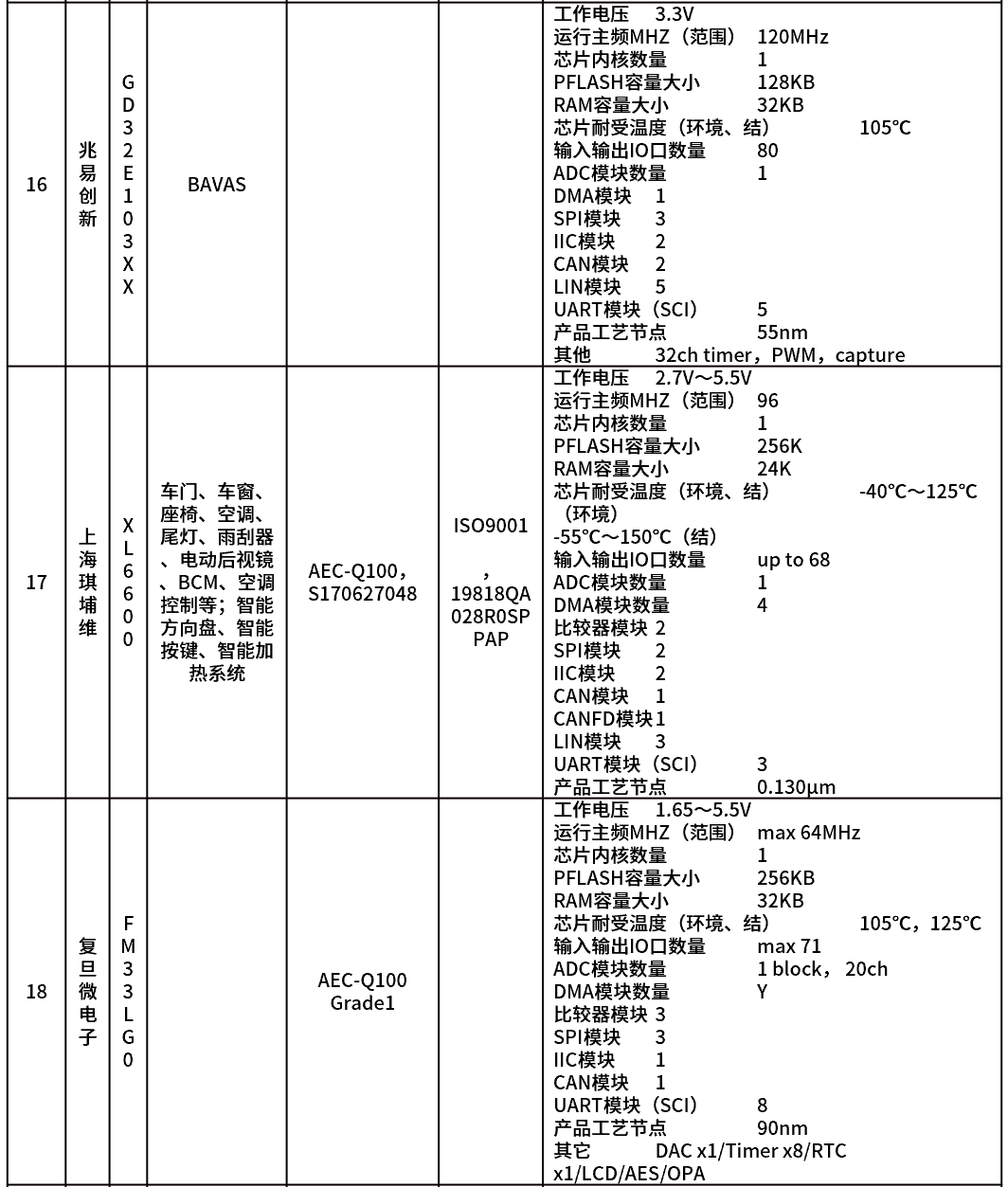

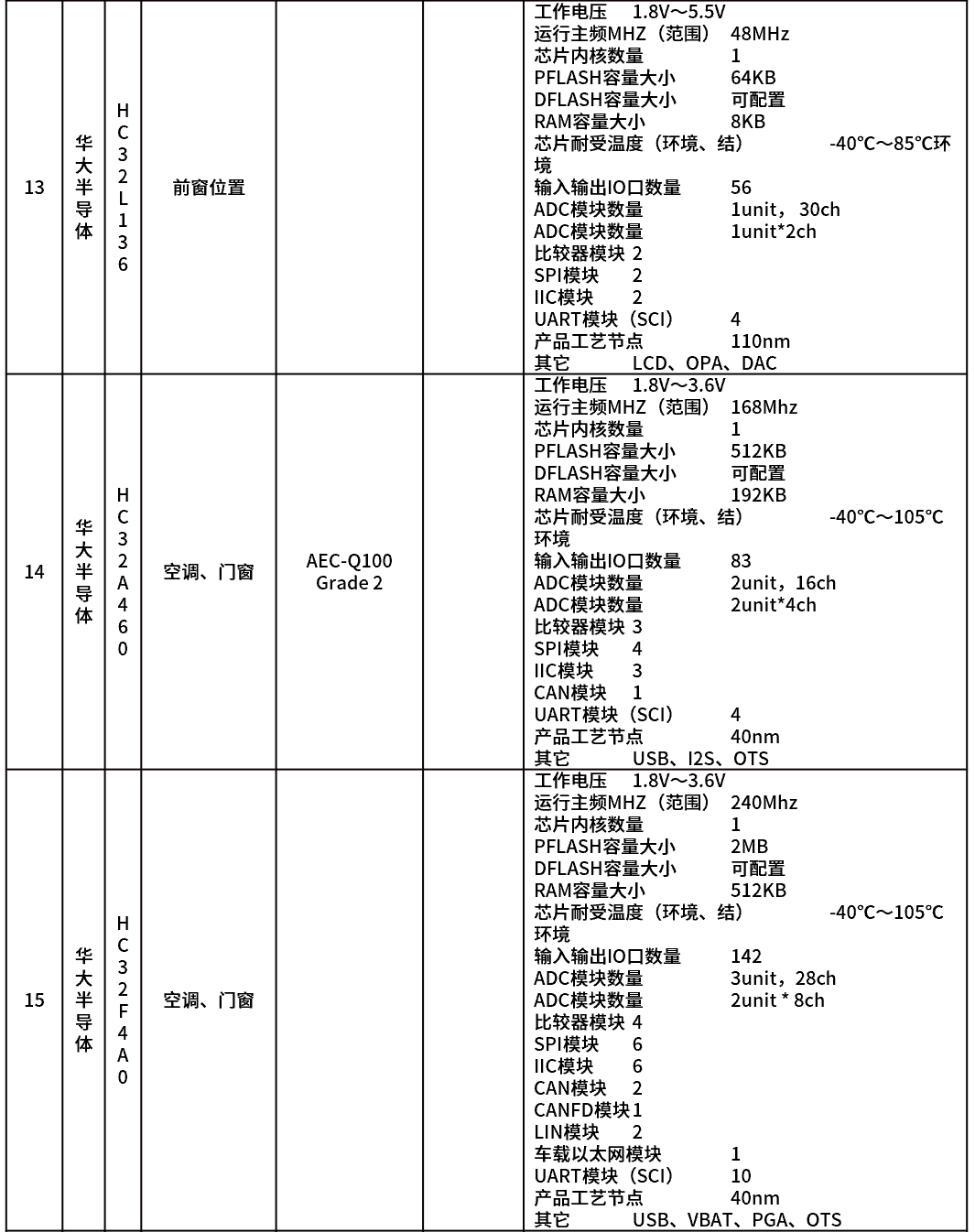

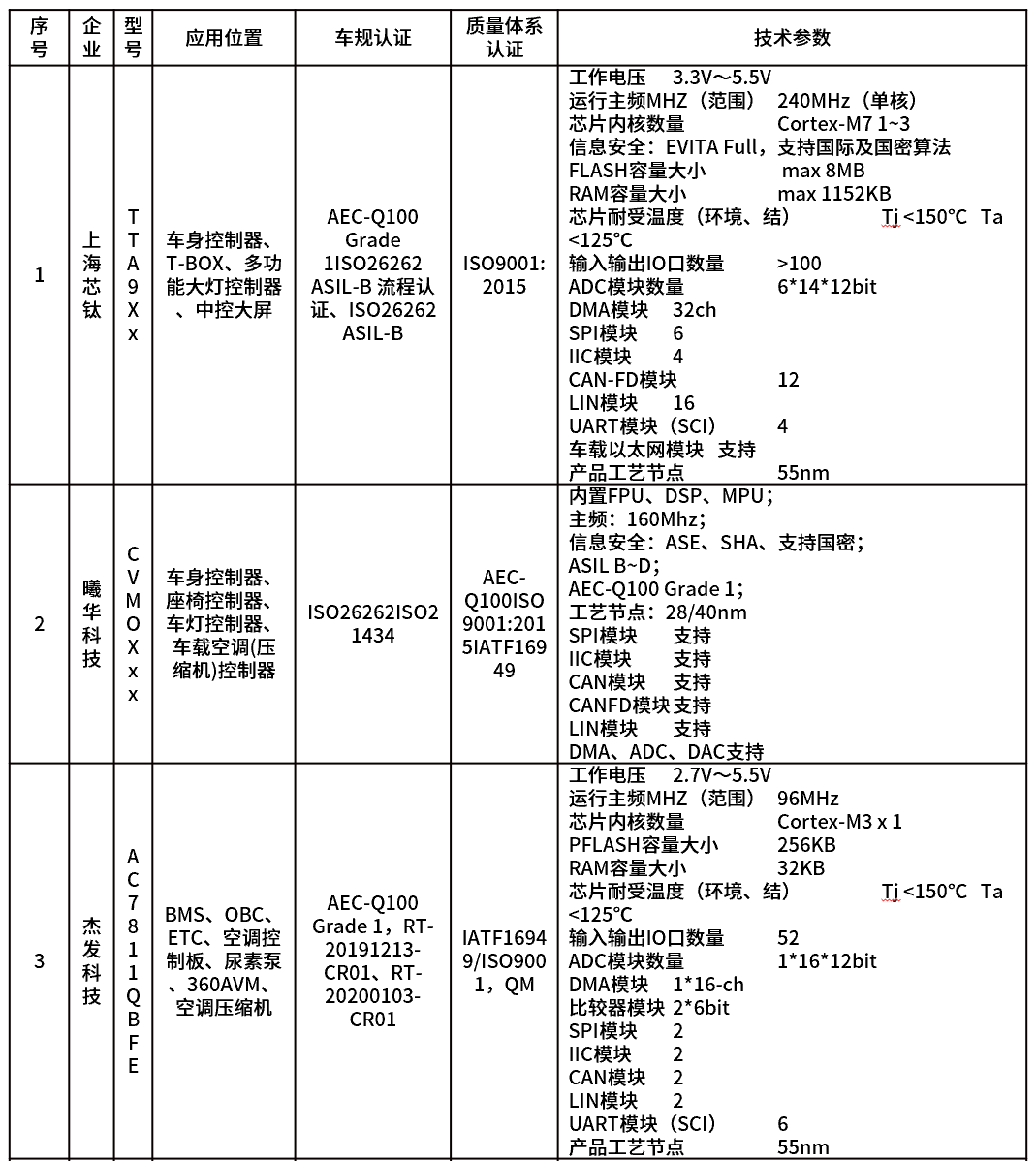

Uwendung vum Haussteierungschip

Autosteierungschips baséieren haaptsächlech op Auto-MCU. Féierend inlännesch Entreprisen wéi Ziguang Guowei, Huada Semiconductor, Shanghai Xinti, Zhaoyi Innovation, Jiefa Technology, Xinchi Technology, Beijing Junzheng, Shenzhen Xihua, Shanghai Qipuwei, National Technology, etc., hunn all MCU-Produktsequenzen a Autosgréisst, déi sech mat auslännesche Risenprodukter vergläichen a momentan op der ARM-Architektur baséieren. E puer Entreprisen hunn och Fuerschung an Entwécklung vun der RISC-V-Architektur duerchgefouert.

Aktuell gëtt den inlännesche Chip fir d'Kontroll vun de Gefierer haaptsächlech am Automobilmaart fir d'Frontladung benotzt a gouf am Beräich vun der Karosserie an dem Infotainment op Autoen ugewannt. Am Beräich vum Chassis, der Energieversuergung an anere Beräicher gëtt en nach ëmmer vun auslännesche Chipgiganten wéi stmicroelectronics, NXP, Texas Instruments a Microchip Semiconductor dominéiert, an nëmmen e puer inlännesch Entreprisen hunn Uwendungen an der Masseproduktioun realiséiert. Aktuell wäert den inlännesche Chiphersteller Chipchi am Abrëll 2022 héichperformant Kontrollchipprodukter aus der E3-Serie op Basis vun ARM Cortex-R5F erausbréngen, mat engem funktionelle Sécherheetsniveau, deen ASIL D erreecht, en Temperaturniveau, deen AEC-Q100 Grad 1 ënnerstëtzt, eng CPU-Frequenz bis zu 800 MHz a bis zu 6 CPU-Kären. Et ass dat performantst Produkt am bestehenden Masseproduktiouns-MCU fir Gefierer a fëllt d'Lück am inlännesche Maart fir héichwäerteg Gefierer a Sécherheet. Mat héijer Leeschtung an héijer Zouverlässegkeet kann en a BMS, ADAS, VCU, By-Wire-Chassis, Instrumenter, HUD, intelligente Réckspigel an anere Kärberäicher fir Gefierer agesat ginn. Méi wéi 100 Clienten hunn E3 fir Produktdesign adoptéiert, dorënner GAC, Geely, etc.

Uwendung vun den Haaptprodukter fir Hauscontroller

Zäitpunkt vun der Verëffentlechung: 19. Juli 2023