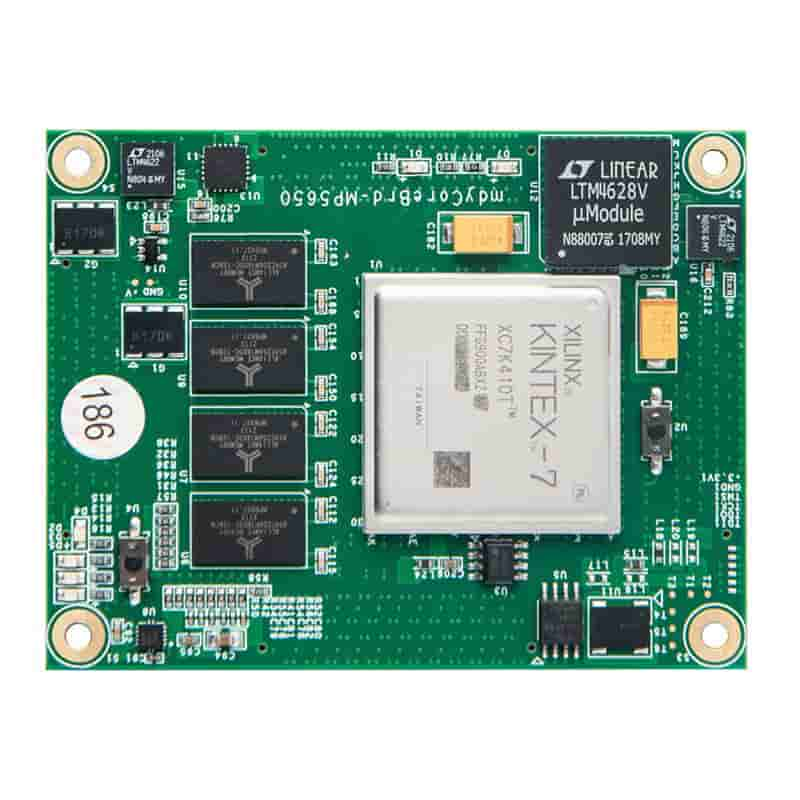

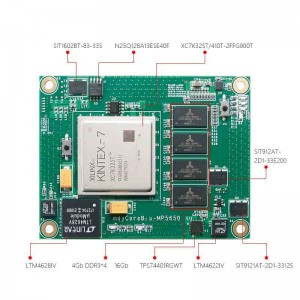

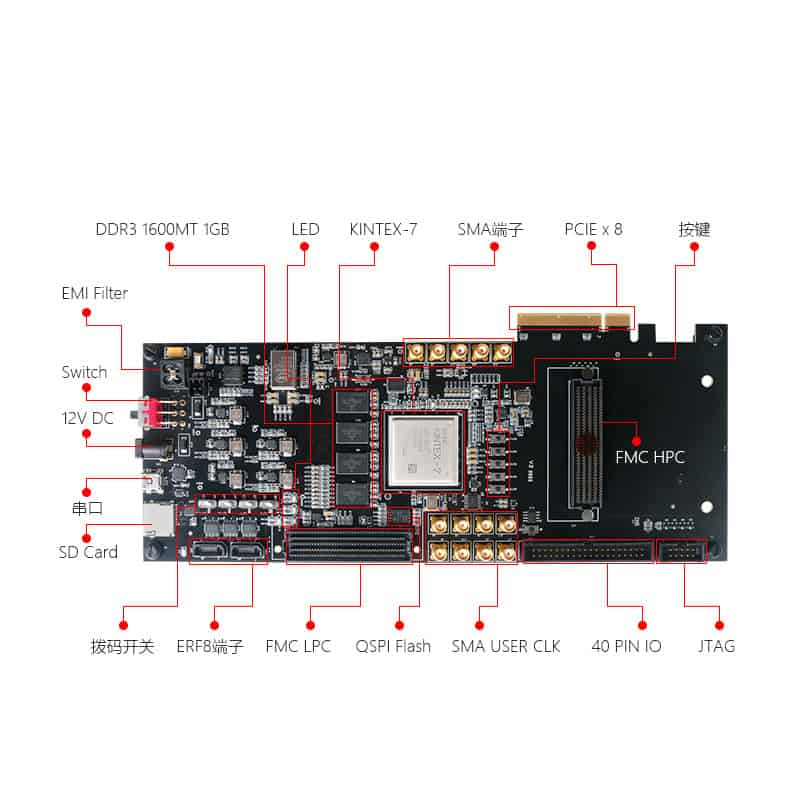

FPGA Xilinx-K7 Kintex7 Xc7k325 410t Industriequalitéit

DDR3 SDRAMQ: 16GB DDR3, 4GB pro Stéck, 16bit Data Bit Data Bid SPI Flash: Een Stéck 128MBITQSPIFLASH, deen fir FPGA Konfiguratiounsdateien a Benotzerdatenspeicher benotzt ka ginn FPGA Bank Interface Niveauen: justierbar 1.8V, 2.5V, 3.3V elektresch Wann Dir den Niveau musst ersetzen, musst Dir nëmmen déi entspriechend Positioun vun der Magnéitperl ersetzen fir d'Upassung z'erreechen. Kärplat Stroumversuergung: 5V-12V Beräich vun der Stroumversuergung EEPROM; M24C02-WMN6TP baséiert op engem I2C Busapparat. No der Startmethod vun der Kärplat vum Second-Line Protokoll: ënnerstëtzt zwee Startmodi, nämlech JTAG, QSPI Flash Stecker. Verlängerte Port, 120pin, Panasonic AXK5A2137yg MP5700 ënnescht Plack SFP Interface: 2 optesch Moduler kënnen eng héich Geschwindegkeet vun der Glasfaserkommunikatioun erreechen, bis zu 6GB/s ënnescht Plack Takt: 1 200MHz Referenztakt ugeschloss un d'Core Board MRCC Taktröhrefuuss, 1 125MHz D'GTX Taktröhreféiss ënnen Plack vun der Takt, déi un d'Core Board ugeschloss ass, ass e 40-Pin Expansiounsport: reservéiert en 2,54mm Standardofstand 40-Shot Verlängerungsport, deen benotzt gëtt fir de Modul vum Client unzeschléissen. Essence Core Board Takt: et gi verschidde Taktquellen op der Platin. Dës enthalen d'200MHz Systemtakt, d'125MHz GTX Takt an d'66MHz EMCCLK Takt. JTAG-Port: 10 Stéck 2,54 mm Standard-JTAG-Port, fir den Eroflueden an d'Debugging vun LEDs fir FPGA-Programmer: insgesamt 6 rout LED-Luuchten am Kärplat, déi d'Stroumversuergung vun der Platenkaart uginn, 4 Signalindikatorluuchten a FPGA IO-Röhreféiss direkt ugeschloss Schlëssel: 4 Schlësselen. 4 Schlësselen. Dëst sinn FPGA-Reset-Knäppercher, Program_b-Knäppercher an zwou Benotzerknäppercher

A: PCB: Quantitéit, Gerber-Datei an technesch Ufuerderungen (Material, Uewerflächenbehandlung, Kupferdicke, Platendéck,...).

PCBA: PCB-Informatiounen, BOM, (Testdokumenter...).

A: Gerber-Datei: CAM350 RS274X

PCB-Datei: Protel 99SE, P-CAD 2001 PCB

Stichplang: Excel (PDF, Word, txt).

A: Är Dateie ginn a voller Sécherheet gespäichert. Mir schützen d'intellektuellt Eegentum vun eise Clienten am ganze Prozess. All Dokumenter vun eise Clienten ginn ni mat Drëttpersounen gedeelt.

A: Et gëtt kee MOQ. Mir kënnen souwuel kleng wéi och grouss Volumenproduktioune mat Flexibilitéit handhaben.

A: D'Versandkäschte ginn duerch d'Destinatioun, d'Gewiicht an d'Verpackungsgréisst vun de Wueren bestëmmt. Sot eis w.e.g. Bescheed, wann Dir eng Offer fir d'Versandkäschte braucht.

A: Jo, mir kënnen d'Komponentquell ubidden, a mir akzeptéieren och Komponente vum Client.

Produktkategorien

-

Telefon

-

E-Mail

-

WhatsApp

-

Skype

-

Skype

-

Skype