Halen dës PCB wiring Punkten am Kapp

1. Allgemeng Praxis

Am PCB Design, fir den Héichfrequenz Circuit Verwaltungsrot Design méi raisonnabel ze maachen, besser Anti-Interferenz Leeschtung, soll aus de folgenden Aspekter considéréiert ginn:

(1) raisonnabel Auswiel vu Schichten Beim Routing vun Héichfrequenz Circuitboards am PCB Design, gëtt de banneschten Fliger an der Mëtt als Kraaft- a Buedemschicht benotzt, wat eng Schëldroll spille kann, effektiv d'parasitär Induktioun reduzéieren, d'Längt vun der Längt verkierzen. Signallinnen, a reduzéieren d'Kräizinterferenz tëscht Signaler.

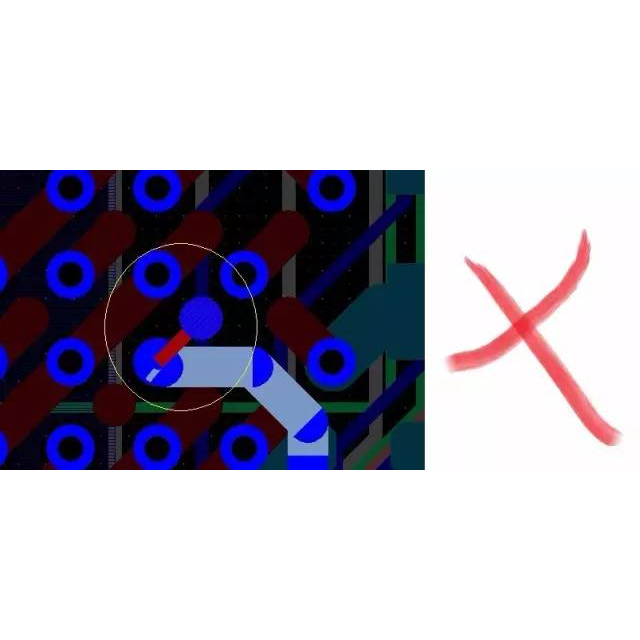

(2) Routing Modus Routing Modus muss am Aklang mat 45 ° Wénkel dréien oder Bogen dréien, déi héich-Frequenz Signal Emissioun a géigesäitege Kopplung reduzéieren kann.

(3) Kabellängt Wat méi kuerz ass d'Kabellängt, wat besser.Wat méi kuerz ass d'parallel Distanz tëscht zwee Drot, wat besser.

(4) Zuel vun duerch Lächer Déi manner Zuel vun duerch Lächer, der besser.

(5) Interlayer wiring Richtung D'Richtung vun interlayer wiring soll vertikal sinn, dat ass, déi iewescht Layer ass horizontal, déi ënnescht Layer ass vertikal, sou wéi d'Interferenz tëscht Signaler reduzéieren.

(6) Kupferbeschichtung erhéicht Buedem Kupferbeschichtung kann d'Interferenz tëscht Signaler reduzéieren.

(7) D'Inklusioun vun der wichteger Signallinnveraarbechtung, kann d'Anti-Interferenzfäegkeet vum Signal wesentlech verbesseren, natierlech kann och d'Inklusioun vun der Interferenzquellveraarbechtung sinn, sou datt et net mat anere Signaler stéiert.

(8) Signal Kabelen Streck keng Signaler an Schleifen.Route Signaler am Daisy Kette Modus.

2. Wiring Prioritéit

Schlëssel Signal Linn Prioritéit: Analog kleng Signal, Héich-Vitesse Signal, Auer Signal an Synchroniséierung Signal an aner Schlëssel Signaler Prioritéit wiring

Dicht éischt Prinzip: Start wiring vun de stäerkste komplex Verbindungen op der Verwaltungsrot.Start wiring vun der dichtst wiring Beräich vun der Verwaltungsrot

Punkten ze notéieren:

A. Probéieren eng speziell wiring Layer fir Schlëssel Signaler wéi Auer Signaler ze bidden, héich-Frequenz Signaler a sensibel Signaler, a garantéieren de Minimum Loop Beräich.Wann néideg, manuell Prioritéit wiring, shielding an Erhéijung Sécherheet Abstand soll ugeholl ginn.Sécherstellen Signal Qualitéit.

b.EMC Ëmfeld tëscht der Kraaftschicht an dem Buedem ass schlecht, sou datt d'Signaler empfindlech op Stéierungen vermeit ginn.

c.D'Netz mat Impedanz Kontroll Ufuerderunge soll sou wäit wéi méiglech no der Linn Längt an Linn Breet Ufuerderunge kabelt ginn.

3, Auer wiring

D'Auerlinn ass ee vun de gréisste Faktoren déi EMC beaflossen.Maachen manner Lächer an der Auer Linn, vermeiden Spadséiergank mat anere Signal Linnen sou wäit wéi méiglech, a bleiwen ewech vun allgemenge Signal Linnen Stéierungen mat Signal Linnen ze vermeiden.Zur selwechter Zäit sollt d'Energieversuergung um Bord vermeit ginn fir Interferenz tëscht der Energieversuergung an der Auer ze verhënneren.

Wann et eng speziell Auer Chip op der Verwaltungsrot ass, kann et net ënnert der Linn goen, soll ënnert der Koffer geluecht ginn, wann néideg, kann och speziell zu sengem Land ginn.Fir vill Chip Referenz Kristallsglas produzéiert Oszilléierer sollen dës Kristallsglas produzéiert net ënnert der Linn ginn, Koffer Isolatioun ze leeën.

4. Linn am richtege Wénkel

Richteg-Wénkel cabling ass allgemeng néideg der Situatioun am PCB wiring ze vermeiden, an ass bal ee vun de Standarden ginn der Qualitéit vun wiring ze moossen, sou wéi vill Impakt wäert Recht-Wénkel cabling op Signal Transmissioun hunn?Prinzipiell wäert d'Rechtwénkelrouting d'Linnbreed vun der Transmissiounslinn änneren, wat zu Impedanzdiskontinuitéit resultéiert.Tatsächlech, net nëmme richteg Wénkel Routing, Tonne Wénkel, akut Wénkel Routing kann Impedanz Ännerungen Ursaach.

Den Afloss vum richtege Wénkel Routing op Signal gëtt haaptsächlech an dräi Aspekter reflektéiert:

Als éischt kann den Eck mat der kapazitiver Belaaschtung op der Transmissiounslinn gläichwäerteg sinn, d'Steigerzäit verlangsamt;

Zweetens, Impedanzdiskontinuitéit wäert Signalreflexioun verursaachen;

Drëttens, EMI produzéiert vum richtege Wénkel Tipp.

5. Akute Wénkel

(1) Fir Héichfrequenzstroum, wann de Wendepunkt vum Drot e richtege Wénkel oder souguer en akuten Wénkel presentéiert, no bei der Ecke, ass d'magnetesch Fluxdicht an d'elektresch Feldintensitéit relativ héich, wäert d'Strahlung staark elektromagnéitesch Welle, an d'Induktioun hei wäert relativ grouss ginn, der inductive wäert méi grouss wéi de stompegen Wénkel oder ofgerënnt Wénkel.

(2) Fir de Busverdrahtung vum digitale Circuit ass d'Verdrahtungseck stompeg oder ofgerënnt, d'Gebitt vun der Drot ass relativ kleng.Ënnert der selwechter Linn Ofstand Conditioun, hëlt den Total Linn Ofstand 0,3 Mol manner Breet wéi de richtege Wénkel Wendung.

6. Differenziell Routing

Vgl.Differentialkabel an Impedanzmatching

Differential Signal gëtt ëmmer méi verbreet am Design vun High-Speed Circuits benotzt, well déi wichtegst Signaler a Circuiten ëmmer Differentialstruktur benotzen.Definitioun: Am einfachen Englesch heescht et datt de Chauffer zwee gläichwäerteg, invertéierend Signaler schéckt, an den Empfänger bestëmmt ob de logesche Staat "0" oder "1" ass andeems den Ënnerscheed tëscht den zwou Spannungen vergläicht.De Pair, deen den Differentialsignal droen, gëtt Differentialrouting genannt.

Am Verglach mam gewéinleche Single-End Signal Routing huet Differentialsignal déi offensichtlech Virdeeler an de folgenden dräi Aspekter:

a.Staark Anti-Interferenzfäegkeet, well d'Kupplung tëscht den zwee Differentialleitungen ganz gutt ass, wann et Kaméidiinterferenz vu bausse gëtt, ass et bal un déi zwou Linnen gläichzäiteg gekoppelt, an den Empfänger këmmert sech nëmmen ëm den Ënnerscheed tëscht dem zwee Signaler, sou datt de gemeinsame Modus Kaméidi vu baussen komplett annuléiert ka ginn.

b.kann effektiv EMI hemmen.Ähnlech, well d'Polaritéit vun zwee Signaler entgéintgesat ass, kënnen d'elektromagnetesch Felder, déi vun hinnen ausgestraalt ginn, géigesäiteg annuléieren.Wat méi no d'Kopplung ass, wat manner elektromagnetesch Energie op d'Äussewelt fräigesat gëtt.

c.Präzis Timing Positionéierung.Zënter datt d'Schalterännerunge vun Differentialsignaler op der Kräizung vun zwee Signaler lokaliséiert sinn, am Géigesaz zu gewéinleche Single-End Signaler, déi op héich an niddreg Schwellspannung vertrauen, ass den Impakt vun der Technologie an der Temperatur kleng, wat d'Feeler am Timing reduzéiere kann a méi ass. gëeegent fir Circuiten mat niddereg Amplituden Signaler.LVDS (Nidderegspannungsdifferentialsignaléierung), déi am Moment populär ass, bezitt sech op dës kleng Amplituden Differentialsignaléierungstechnologie.

Fir PCB Ingenieuren ass dat Wichtegst fir sécherzestellen datt d'Virdeeler vum Differentialrouting voll an der aktueller Routing genotzt kënne ginn.Vläicht soulaang de Kontakt mat Layout Leit d'allgemeng Ufuerderunge vun der Differentialrouting verstoen, dat heescht "gläich Längt, gläich Distanz".

Déi gläich Längt ass fir sécherzestellen datt déi zwee Differentialsignaler zu all Moment entgéintgesate Polaritéit behalen an de gemeinsame Moduskomponent reduzéieren.Equidistanz ass haaptsächlech fir sécherzestellen datt d'Differenzimpedanz konsequent ass a Reflexioun reduzéieren."Sou no wéi méiglech" ass heiansdo eng Fuerderung fir differenziell Routing.

7. Schlaang Linn

Serpentine Linn ass eng Aart Layout déi dacks am Layout benotzt gëtt.Säin Haaptzweck ass d'Verzögerung unzepassen an den Ufuerderunge vum System Timing Design ze treffen.Déi éischt Saach, déi Designer musse realiséieren, ass datt Schlaangähnlech Drot d'Signalqualitéit zerstéiere kënnen an d'Transmissiounsverzögerung änneren, a sollten vermeit ginn wann se wiring.Wéi och ëmmer, am aktuellen Design, fir genuch Haltzäit vu Signaler ze garantéieren, oder fir d'Zäitoffset tëscht der selwechter Grupp vu Signaler ze reduzéieren, ass et dacks néideg bewosst ze wanderen.

Punkten ze notéieren:

- Pairen vun Differenziell Signal Linnen, allgemeng parallel Linnen, sou wéineg wéi méiglech duerch d'Lach, musse ausgepöppelt ginn, sollen zwou Linnen zesummen sinn, fir Impedanzmatching z'erreechen.

- Eng Grupp vu Bussen mat deene selwechte Attributer soll sou wäit wéi méiglech niewentenee gefouert ginn, fir déiselwecht Längt z'erreechen.D'Lach déi vum Patch Pad féiert ass sou wäit wéi méiglech vum Pad ewech.