Am Allgemengen ass et schwéier, e klenge Feeler bei der Entwécklung, Produktioun an dem Gebrauch vun Hallefleiterkomponenten ze vermeiden. Mat der kontinuéierlecher Verbesserung vun den Ufuerderunge fir d'Produktqualitéit gëtt d'Feeleranalyse ëmmer méi wichteg. Duerch d'Analyse vu spezifesche Feelerchips kann et de Circuitdesigner hëllefen, Mängel am Apparatdesign, d'Iwwereneestëmmung vun de Prozessparameteren, den onraisonnabelen Design vun de Peripheriekreesser oder d'Feelerbedienung, déi duerch de Problem verursaacht ginn, ze fannen. D'Noutwennegkeet vun der Feeleranalyse vun Hallefleiterkomponenten manifestéiert sech haaptsächlech an de folgende Aspekter:

(1) D'Feeleranalyse ass e néidegt Mëttel fir de Feelermechanismus vum Chip vum Apparat ze bestëmmen;

(2) D'Feeleranalyse liwwert déi néideg Basis an Informatiounen fir eng effektiv Feelerdiagnos;

(3) D'Feeleranalyse liwwert néideg Feedbackinformatioune fir Designingenieuren, fir den Chipdesign kontinuéierlech ze verbesseren oder ze reparéieren an en am Aklang mat der Designspezifikatioun méi vernünfteg ze maachen;

(4) D'Feeleranalyse kann déi néideg Ergänzung fir de Produktiounstest sinn a kann déi néideg Informatiounsbasis fir d'Optimiséierung vum Verifizéierungstestprozess liwweren.

Fir d'Feeleranalyse vun Hallefleiterdioden, Audionen oder integréierte Schaltungen, sollten d'elektresch Parameter als éischt getest ginn, an no der Erscheinungsinspektioun ënner dem optesche Mikroskop soll d'Verpakung ewechgeholl ginn. Wärend d'Integritéit vun der Chipfunktioun erhale bleift, sollten déi intern an extern Leitungen, d'Verbindungspunkten an d'Uewerfläch vum Chip sou wäit wéi méiglech erhale bleiwen, fir sech op den nächste Schrëtt vun der Analyse virzebereeden.

Mat Hëllef vu Rasterelektronemikroskopie an Energiespektrum fir dës Analyse: dorënner d'Observatioun vun der mikroskopescher Morphologie, d'Sich no Feelerpunkten, d'Observatioun an d'Lokalisatioun vun Defektpunkten, d'genee Miessung vun der mikroskopescher Geometriegréisst vum Apparat an der Potenzialverdeelung vun der rauer Uewerfläch an d'Logikbeurteilung vum digitale Gate-Circuit (mat der Spannungskontrast-Bildmethod); Fir dës Analyse mat Hëllef vun engem Energiespektrometer oder engem Spektrometer, gëtt folgendes gemaach: Analyse vun der mikroskopescher Elementzesummesetzung, Analyse vun der Materialstruktur oder der Verschmotzungsanalyse.

01. Uewerflächendefekter a Verbrennunge vu Hallefleederkomponenten

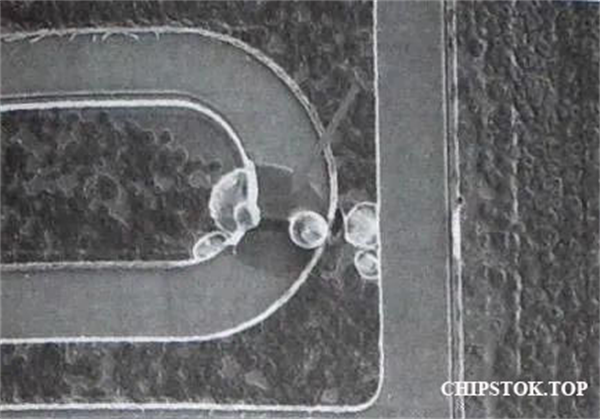

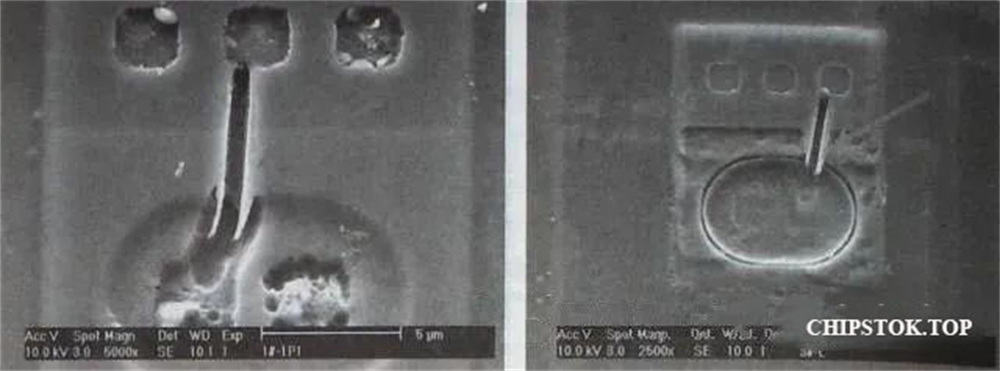

Uewerflächendefekter a Burnout vu Hallefleiterkomponenten sinn allebéid heefeg Ausfallmodi, wéi an der Figur 1 gewisen, wat den Defekt vun der gereinegter Schicht vun engem integréierte Circuit ass.

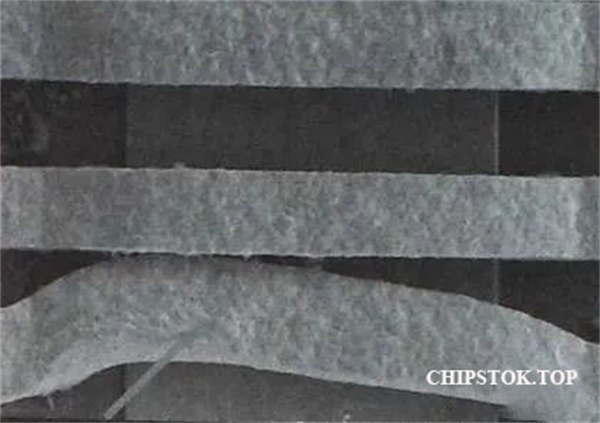

Figur 2 weist den Uewerflächendefekt vun der metalliséierter Schicht vum integréierte Schaltkrees.

Figur 3 weist den Duerchbrochkanal tëscht den zwou Metallsträifen vum integréierte Circuit.

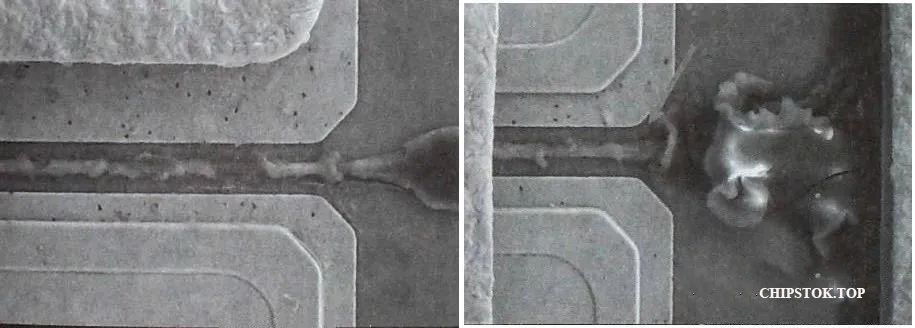

Figur 4 weist den Zesummebroch vum Metallsträifen an d'Schiefdeformatioun op der Loftbréck am Mikrowellenapparat.

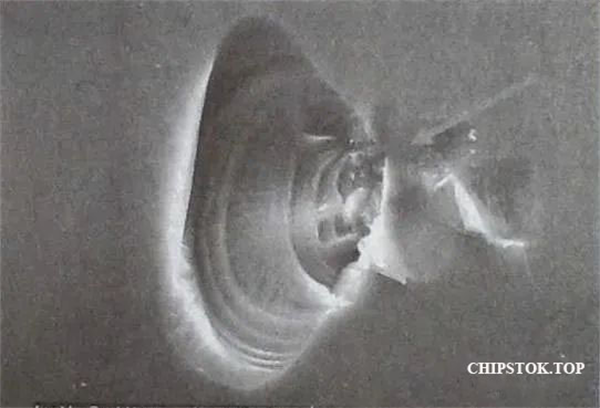

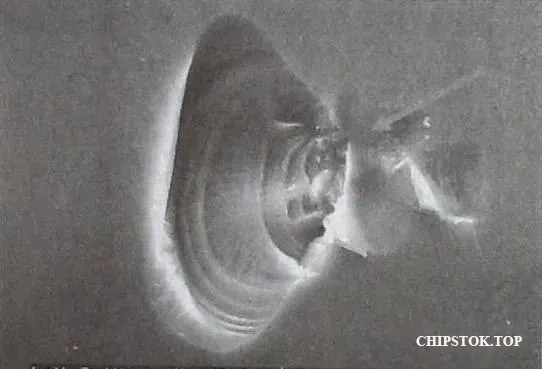

Figur 5 weist de Gitterausbrennen vum Mikrowellenröhr.

Figur 6 weist de mechanesche Schued um integréierten elektresch metalliséierte Drot.

Figur 7 weist d'Öffnung an den Defekt vun der Mesa-Diod-Chip.

Figur 8 weist den Duerchbroch vun der Schutzdiod um Input vum integréierte Circuit.

Figur 9 weist, datt d'Uewerfläch vum integréierte Schaltungschip duerch mechaneschen Impakt beschiedegt ass.

Figur 10 weist de partielle Burnout vum integréierte Schaltungschip.

Figur 11 weist, datt den Diodenchip futti a schwéier verbrannt war, an d'Brechpunkte sinn an e Schmëlzzoustand iwwergaangen.

Figur 12 weist de verbrannte Galliumnitrid-Mikrowellen-Energieröhrchip, an de Verbrennungspunkt weist en geschmollte Sputterzoustand op.

02. Elektrostatesch Duerchfall

Hallefleiterkomponenten, vun der Fabrikatioun, der Verpackung, dem Transport bis zur Aféierung op der Leiterplack, dem Schweessen, der Maschinnemontage an anere Prozesser, si vun der statescher Elektrizitéit bedroht. Dobäi gëtt den Transport duerch heefeg Beweegungen an einfach Belaaschtung duerch déi statesch Elektrizitéit, déi vun der Äussewelt generéiert gëtt, beschiedegt. Dofir sollt besonnesch Opmierksamkeet op den elektrostatesche Schutz während der Iwwerdroung an dem Transport bezuelt ginn, fir Verloschter ze reduzéieren.

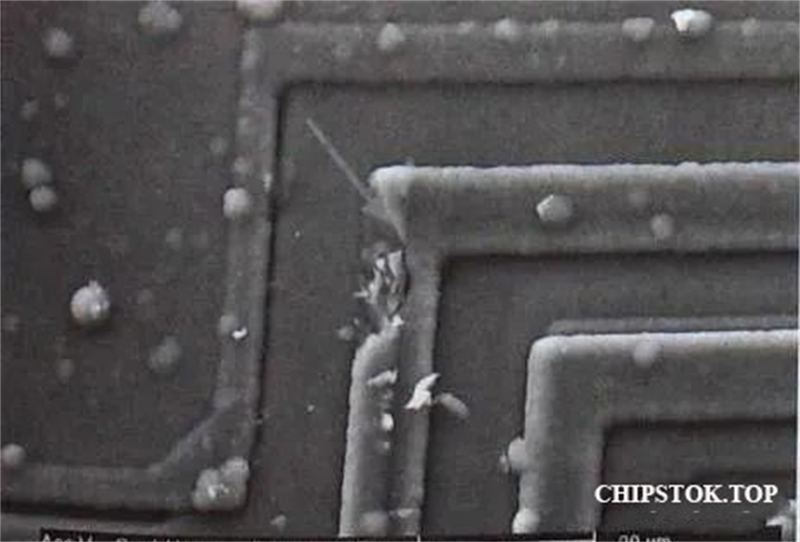

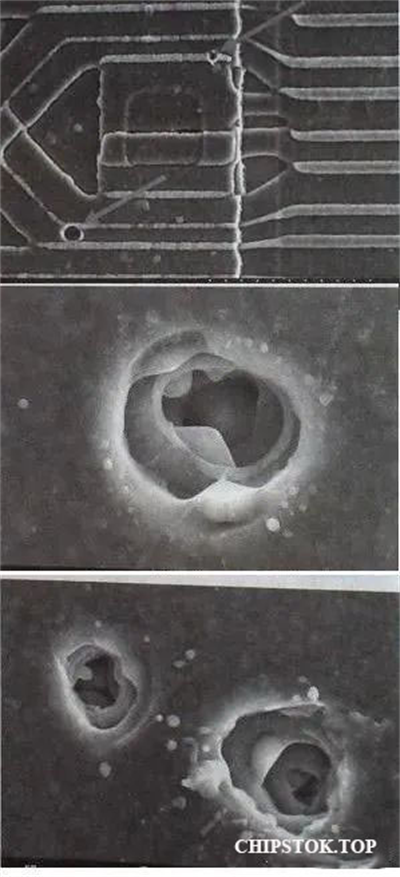

Bei Hallefleiterbaugruppen mat unipolare MOS-Réier an MOS-Integratiounsschaltunge si besonnesch empfindlech op statesch Elektrizitéit, besonnesch MOS-Réier, well hiren eegenen Input-Widderstand ganz héich ass an d'Gate-Source-Elektrodekapazitanz ganz kleng ass. Dofir ass et ganz einfach, vun engem externen elektromagnetesche Feld oder enger elektrostatischer Induktioun beaflosst ze ginn a gelueden ze ginn. Wéinst der elektrostatischer Generatioun ass et schwéier, d'Ladung rechtzäiteg entzelueden. Dofir ass et einfach, datt d'Akkumulatioun vu statescher Elektrizitéit zu engem direkten Duerchbroch vum Baudeel féiert. D'Form vum elektrostateschen Duerchbroch ass haaptsächlech en elektreschen genialen Duerchbroch, dat heescht, déi dënn Oxidschicht vum Gitter gëtt ofgebrach an e Lach bildt, wat d'Lück tëscht dem Gitter an der Quell oder tëscht dem Gitter an dem Drain verkierzt.

An am Verglach zu MOS-Röhren ass d'antistatesch Duerchbrochkapazitéit vun engem MOS-Integréierte Schaltkrees relativ liicht besser, well den Input-Terminal vun der MOS-Integréierter Schaltkrees mat enger Schutzdiod ausgestatt ass. Soubal eng grouss elektrostatesch Spannung oder Iwwerspannung entsteet, kënnen déi meescht Schutzdioden op d'Äerd geschalt ginn, awer wann d'Spannung ze héich ass oder de momentane Verstärkungsstroum ze grouss ass, da falen d'Schutzdioden heiansdo selwer aus, wéi an der Figur 8 gewisen.

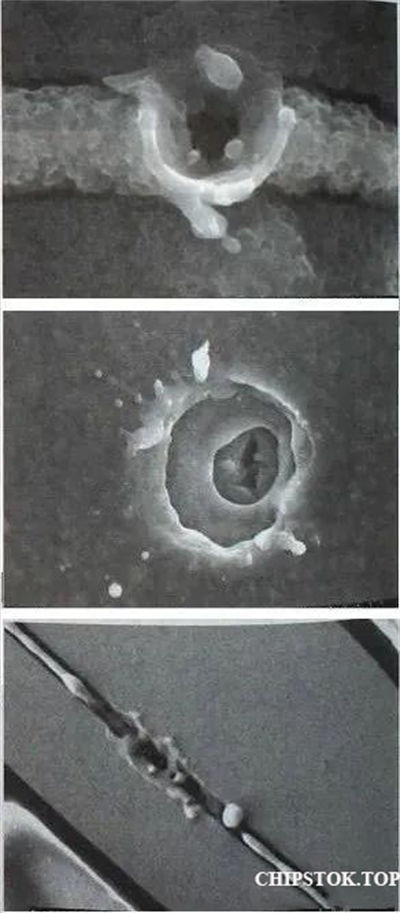

Déi verschidde Biller, déi an der Figur 13 gewise ginn, weisen d'Topographie vum elektrostatesche Duerchbroch vun engem MOS-Integratiounsschaltkrees. Den Duerchbrochpunkt ass kleng an déif, wat en Zoustand vu geschmoltenem Sputtering duerstellt.

Figur 14 weist d'Erscheinung vun engem elektrostateschen Duerchbroch vum Magnéitkapp vun enger Computerfestplack.

Zäitpunkt vun der Verëffentlechung: 08. Juli 2023